使用八进制CMOS缓冲器的二象限乘法DAC

时间:03-14

来源:互联网

点击:

本设计实例使用一个八进制CMOS缓冲器的大工作电压范围,呈现一个由缓冲器/线驱动器IC74HC244组成的简单的八位二象限乘法数字模拟转换器(DAC)。

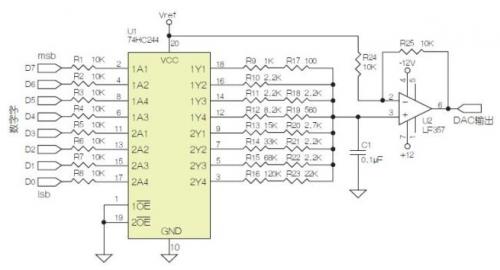

如图1所示,一个八位数字字通过电阻器R1~R8写入CMOS缓冲器U1的八个输入中。U1的各个输出通过由电阻器R9~R23组成的1:2:4:8……128加权电阻网络产生。DAC参考电压Vref馈送给U1VCC,因此,U1的输出电压跟踪Vref的变化。电阻器R1~R8必须要使U1的输出电压免受数字输入的电压水平的影响。

图1 1个八位数字通过电阻器写入CMOS缓冲器中

在U2的引脚3处形成一个八位电压-输出单极DAC,其中Vref等于VCC.C1会视情况低通过滤该输出,而该输出在进行缓冲处理后,乘以因数2进行放大,然后由Vref抵消,进而在运算放大器LF357的引脚6处提供一个双极DAC输出。

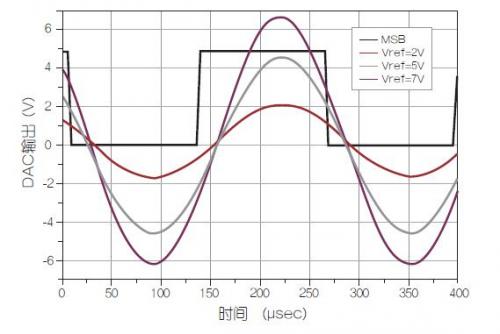

图2 16采样/周期DAC输出,2V-7V参考电压3750Hz合成正弦波

图2给出的是16采样/周期DAC输出,2V~7V参考电压3750Hz合成正弦波。该DAC测量稳定时间为200ns,其中C1取值为200pF.

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)