数字电源 UCD9224 与UCD7232 应用中输出电压关机负过冲的分析及解决

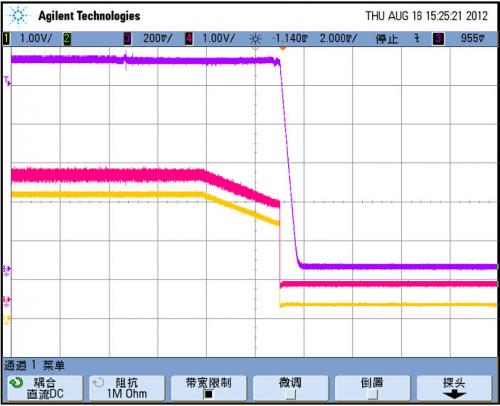

图 7:3.3V 与 SRE 信号

根据UCD9224芯片的硬件设计,其供电电压下降到2.8V时会处于reset模式。而其进入reset模式后,SRE_1A引脚和SRE_1B引脚变更为高阻态,SRE_2A引脚和SRE_3A引脚变为低电平态(被 UCD9224强制拉低到地)。

同时,由于UCD7232芯片内部对SRE管脚有弱上拉(上拉到3.3V),因此,SRE_1A和SRE_1B的电压信号会出现反弹并下降缓慢,而SRE_2A和SRE_3A的电压信号可以迅速下降到0。

4. 解决措施

考虑到SRE_1A和SRE_1B在UCD9224进入reset模式后变为高阻态,引脚电压下降缓慢,因此可以添加下拉电阻以快速拉低上述引脚的电压。下拉电阻的阻值需要小于3.74Kohm,以保证SRE管脚的残留电压低于低电平判定阀值0.9V。

图8显示的是添加两颗下拉电阻(1Kohm)后的关机波形(CH4为SRE_1A;CH1为SRE_1B;CH3为输出电压),负载电流为3A。可以观察到,SRE_1A和SRE_1B在关机过程中没有反弹,而是快速下降到0V。因此,输出电容只通过负载放电,没有负过冲。

|  |

| 图 8:添加下拉电阻后的关机波形图 | 图9:空载关机时的输出电压波形 |

5. 常规供电设计的输出电压负过冲

上述电源系统的特殊之处在于采用了3.3V和12V分开的供电架构。在该应用中,当关闭3.3V后,12V还处于稳定状态,即SRE_1A和SRE_1B进入高阻态后,UCD7232还正常工作,这让BUCK下管长时间导通成为了可能。然而,在采用常规供电设计时,同样会存在负过冲的异常情形。

5.1 常规供电设计及输出电压的负过冲

常规供电架构的设计为3.3V通过LDO由12V转换得来,因此整个电源系统的输入电压只有 12V。图10显示的即为采用常规供电架构设计的数字电源系统框图(局部)。

图9显示的是关闭12V时的关机波形(CH1为输出电压,CH3为SRE_1B),输出端空载。可以观察到,当关机动作发生后(对应于SRE_1B下降到0的时刻),由于是空载,输出电压几乎保持不变;经过大约2.8ms后,SRE_1B又上升,此时,输出电压快速下降到0V,并伴随有负过冲。

图 10:常规供电架构设计(局部)

5.2 输出电压的负过冲分析及结论

基于本文之前的分析,怀疑图9中 SRE_1B下降到0之后的上升依然是因为UCD9224 进入reset模式而使SRE_1B变为高阻导致。基于此,展开测试与分析。

图11测试了关机时12V(CH3),SRE_1B(CH4)和SRE_2A(CH1)的波形。可以观察到,SRE_1B再次变为高的时刻,SRE_2A依然保持为低。

图12测试了关机时V33D(CH4,3.3V),BPCAP(CH1,1.8V)和SRE_1B(CH3)的波形。可以观察到SRE_1B再次变高的时刻,UCD9224的3.3V下降到了2.6V左右,芯片处于reset 模式。

综合上述信息可知,常规供电架构设计中,空载关机时的输出电压负过冲依然是由于 SRE_1A和SRE_1B进入了高阻态导致。为消除该负过冲,同样可以在SRE_1A和SRE_1B引脚添加下拉电阻来完成。

| |

| 图11:SRE_1B和SRE_2A引脚的波形 | 图12:SRE_1B,3.3V和1.8V的波形 |

5.3 其它规避措施

在关机动作发生后,12V电压逐渐下降,会首先触发欠压保护(欠压保护点由软件设置),系统关机,DPWM和SRE被拉低,输出关闭;随着12V的继续下降,触发UCD7232的欠压保护,FLT引脚变为高,并上报给UCD9224。图13完整的显示了上述过程。(图13的CH4为3.3V电压波形,CH3为SRE_1B引脚信号,CH1为FLT引脚信号)

由该波形可知,SRE_1B再次上升时,由于UCD7232还处于正常工作状态(FLT还为低),因此BUCK下管可以正常导通,造成输出电压的负过冲。如果将系统欠压保护点设置的略低一些,或减缓3.3V的下降速度,以保证UCD9224进入reset模式时,UCD7232已经处于欠压保护状态,则输出电压的负过冲亦可以避免。

图 13:SRE_1B 与 FLT

为减缓3.3V的下降速度,可使用Dropout电压较小的LDO,如TPS79333(VDROPOUT=0.18V)。由图11和图12对比可知,当前方案下使用的LDO具有较大的Dropout 电压(6.9V-2.6V=4.3V)。如使用TPS79333,当UCD7232触发4.1V欠压保护停止工作时,UCD9224仍能得到稳定的3.3V供电,也就避免了进入reset模式。

6. 结论

在只关闭3.3V的应用场景中,输出端无论是否带载,输出电压都会出现负过冲;而在采用常规供电设计的系统中,关闭12V时,如果输出端空载,同样会出现负过冲问题。输出电压负过冲的根因是UCD9224在处于reset模式后,SRE_1A和SRE_1B引脚变为高阻态,其电压有反弹并下降缓慢导致。解决措施是在SRE_1A和SRE_1B引脚各增加一颗下拉电阻。实测发现,该解决措施简单有效。

7. 参考文献

1. UCD9224 datasheet,

UCD9224 数字电源 UCD7232 负过冲 德州仪器 相关文章:

- 以数字方式管理电源的简便方法(11-30)

- 热插拨和数字电源监控常见问答(01-18)

- PMBus——数字电源开放标准协议(01-18)

- 智能化数字电源系统的优化设计(02-12)

- 基于FPGA的高精度数字电源(02-12)

- 数字电源控制指南(06-26)