基于EMIRR规范的EMI问题解决方案

随着技术的进步,EMI 对电路正常运行构成越来越大的威胁。这是因为电子应用正转向各种无线通信或者便携式平台。因此大多数干扰 EMI 信号最终都以传导 EMI 的形式进入到 PCB 线迹(trace)中。

当您努力想要设计出一种抗 EMI 电路时,您会发现,模拟传感器电路往往会成为巨大的 EMI 吸收器。这是因为,传感器电路常常产生低电平信号,并且有许多高阻抗模拟端口。另外,这些电路使用更加紧凑的组件间隔,其让系统更容易截获和传导噪声干扰,从而进入到线迹中。

在这种 EMI 情况下,运算放大器 (op amp) 便会成为一个主要目标。我们在本系列文章的第1部分"EMI 如何通过介质干扰电路"看到了这种效应,此文中图 1 所示 EMI 信号引起 1.5 伏的偏移电压误差!

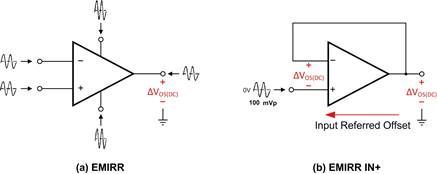

一个标准的运算放大器有 3 个低阻抗引脚(正功率、负功率和输出)以及 2 个高阻抗输入引脚(请参见图 1a)。尽管这些引脚可以抵抗 EMI 影响,但是输入引脚最为脆弱。

图 1 EMIRR 与 EMIRR IN+ 测定方法比较

EMIRR 电磁干扰抑制比

电压反馈放大器的反相和非反相引脚的特性基本相同。但是,非反相输入(请参见图 1b)的放大器 EMI 耐受度测试最为简单。

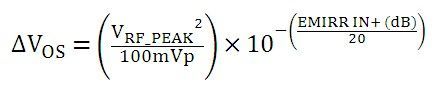

方程式 1

方程式 1 中,VRF_PEAK 为所用 RF 电压的峰值,VOS 为放大器的 DC 偏移电压,而 100 mVP 为 100 mVP 输入信号 EMIRR IN+ 参考。

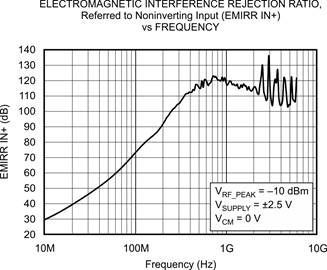

您可以利用 EMIRR 衡量标准,比较放大器的 EMI 抑制性能。图 2 显示了 TI OPA333 CMOS 运算放大器的 EMIRR IN+ 响应。该图表明,这种器件可以较好地抑制器件300 kHz带宽以上的频率信号。

图 2 OPA333、EMRR IN+ 与频率的关系

相比外部 RC 滤波器,集成电路内部 EMI 滤波器拥有三个方面的好处。潜在用户可以对包含集成滤波器的放大器的性能进行测试,以保证其在较宽频率范围的 EMI 抑制性能(2)。无源滤波器组件在寄生电容和电感方面并不理想,其限制了滤波器抑制甚高频噪声的能力。与之形成对比的是,集成电路与片上无源组件的电气特性十分匹配。最后,使用内部滤波器的集成电路还可以给客户带来其它一些好处,例如:组件数目更少、成本更低和电路板面积更小等。

为了降低电路的 EMI 敏感度,电路板设计人员应始终注意使用良好的布局方法。可以通过让线迹长度尽可能的短,使用表面贴装组件,以及使用具有专用信号回路接地层的印制电路板 (PCB),来实现上述目标。尽可能地保持接地层完整,并让数字信号远离模拟信号通路。另外,将射频旁路电容器放置在所有集成电路电源引脚上。让这些电容器靠近器件引脚,并确保在潜在 EMI 频率下其阻抗尽可能地接近 0 欧姆。

- FUJITSU TEN公司采用ADI公司SHARC DSP实现汽车音响系统的声学空间控制(01-12)

- 基于OrCAD/PSpice的信号产生电路设计(04-04)

- VGA旌接RCA接口转换器(04-05)

- 解析PRT自激励振方式VRC软开关变换电源技术(03-13)

- 一种集成RCC式开关电源器件设计及应用(04-16)

- 基于RC正弦波振荡电路的电子琴设计(07-01)