基于RFID标签芯片基带处理器的低功耗设计

的设计

为了降低芯片的功耗,设计中使用了门控时钟:用使能信号控制寄存器的时钟端,当使能信号有效时时钟翻转,否则时钟保持在固定电平。因此时钟使能可以将电路中的部分电路处于空闲状态,阻止寄存器内部翻转和寄存器之间组合逻辑开关动作,以达到节省功耗的目的。图3所示为门控时钟的设计方案。

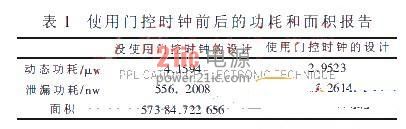

表1给出利用综合工具Design Compiler对当前设计进行综合后的功耗和面积报告。可以看出,本设计使用门控时钟后,总的动态功耗降低了很多,并且在降低功耗的同时,面积也有了一定的减小。

2.4组织模块设计方法

由于在设计中并不是所有的模块都同时工作,而是在某一个状态下,只开启一个或几个模块,其他模块处于关闭状态,所以如果有效组织模块的开关,将会减少寄存器的开关翻转动作。设计中利用有限状态机根据不同的指令和状态转换开启不同的模块来完成数据的处理要求和存储操作:当接收前向数据时,开启编码器、CRC计算/校验、和串并转换;当处理数据时,开启模块有限状态控制机、EEPROM控制模块、静默计数器、随机数产生器;当返回数据时,开启模块有限状态控制机、EEPROM控制模块、数据输出控制端、编码器其他模块关闭。

3、芯片测试

首先采用FPGA完成芯片的功能验证,以FPGA的可编程逻辑阵列为基本单元,实现ISO18000-6B的数字基带功能的硬件仿真验证。然后使用ASIC芯片设计EDA工具将RTL顶层描述映射为基于TSMC提供的目标工艺库的基本数字单元的物理电路,并生成CAD版图且提交给TSMC半导体工厂制作出来。

进行芯片测试时,利用先施阅读器产生RFID各种命令信号,经解调后输入到待测试芯片的数据输入端。芯片在电源、时钟源信号、复位信号的共同激励下进入正常工作状态并对输入命令数据进行响应,将数据输出到调制电路,然后反射回阅读器。阅读器根据接收到的信号决定下一步操作。在阅读器和待测芯片的交互过程中,可用逻辑分析仪观察中间过程。图4为先施阅读器对测试芯片发送read命令时,用逻辑分析仪捕捉的内部信号,其中信号data_in为解调器解调出的前向链路数据,信号data_out为芯片的返回数据。

从已流片芯片的测试结果看,标签芯片数字系统的设计很好地完成了符合ISO18000-6B协议的所有强制命令以及读写操作和锁存、查询锁存等基本功能,且在阅读器存盘操作下的平均速率为45~60张/s,功耗为3.10μW,很好地完成了低功耗无源电子标签的设计。

- RFID在开架书库管理中的应用研究(01-13)

- 一种微波频段有源RFID系统设计(08-23)

- RFID技术分类研究(09-23)

- RFID简介和发展(12-18)

- RFID的分类(01-10)

- 摩佰尔科技RFID智能称重管理系统(10-06)