多路接口与E1协议转换器设计与实现

地址信号,然后使能片癣读信号,这时如果数据总线上有数据,CPU读入数据。但MPC875总线频率高达80 MHz,为了CPU能稳定的读取到数据,这里将片选信号与读信号相"与",然后扩宽3倍得到总线可用信号,在总线可用信号有效期间,数据总线上总有数据,这样,可以保证CPU能稳定的读到数据。

当CPU写入数据时,CPU先给出地址信号,然后给出片选及写信号,在写信号有效期间,CPU稳定的给出数据。因此,在片选及写信号有效时,锁存数据总线上的数据即可。

2.2 CPLD硬件接口电路设计

CPLD主要完成V.35,RS 449,RS 232数据收发;keyboard,LED控制;FIFO读写等功能。功能框图如图5所示。

CPU通过CPLD对接口芯片进行模式选择。V.35,RS 449为同步平衡接口,常用接口速率为N×64 Kb/s(N=1~32)。时钟、数据信号为两线平衡传输,控制信号为不平衡传输。发送数据时,将与之对应的时钟一并输出。在接收数据时,用接口时钟采样数据。

RS 232为不平衡传输。帧格式固定为:1位开始位、8位数据位、结束位。结束位有三种:1位、1.5位、2位。开始位固定为"0",停止位固定为"1"。通信双方在开始通信前必须约定好串行传输的参数(传输速度、帧格式)。在发送端,首先通过分频产生需要的串行波特率,然后按照帧格式以约定好的速率发送。在接收端,使用8倍于波特率的时钟对接收到的信号进行过采样,经过滤波后如果为低电平信号,即认为是开始位,然后按照约定好的速率接收数据。

在接收数据时,FIFO读写模块将串行接收数据变成8位并行,同时,将与接收数据同步的时钟8分频,用此时钟将8位并行数据写入与该接口对应的FIFO;在发送数据时,将发送时钟8分频,用此时钟从与该接口对应的FIFO读取数据,同时将8位并行数据串行输出。

keyboard为4×4扫描式矩阵键盘,具有16个键。由硬件程序自动扫描键盘,输入数据触发中断,CPU读取数据。LED输出由CPU写入相应的显示寄存器,然后硬件程序将相关信号输出点亮LED。

2.3 FPGA硬件电路设计

FPGA主要根据时隙的分配设置,在时钟系统的管理控制下,完成E1的编解帧功能。功能框图如图6所示。

CPU根据设置向时隙分配寄存器写入相应的数据。在发送数据时,E1编解帧模块根据时隙分配设置,从相应的FIFO读取数据,写入该时隙。对于没有使用的空时隙,按照空时隙处理办法填入无效数据。发送时钟为FPGA外接的2.048 MHz时钟。由于XRT82D20为数据差分输入,因此将编解帧模块输出的数据TPOS进行反向得到TNEG,平衡输出。TCLK为发送时钟。

在接收时,XRT82D20数据差分输入RPOS,RNEG,将两个信号相减得到输入数据信号,RCLK为时钟输入。在输入时钟的控制下,E1编解帧模块将数据解帧。同时,根据时隙分配设置,将各个时隙的数据送入不同的接口FIFO。

3 软件主程序流程图

MPC875主要完成接口芯片初始化设置、时隙分配设置输入、状态显示等功能。

上电以后,CPU进行初始化设置。延迟1 ms进行内存地址分配:每个自定义寄存器及I/O均分配一个内存地址,CPU操作时读写相应地址即可;接着进行LTC1546/LTC1544模式选择,将三组接口分别配置为V.35,RS 449,RS 232;然后查询时隙分配设置输入,如果已经输入时隙分配设置,则读取时隙设置数据,否则,等待时隙设置输入;协议转换器初始化设置完毕,每隔100 ms进行一次线路运行状态告警显示。

4 协议转换器测试

4.1 测试平台搭建

测试平台由JDSU ANT-5 SDH接入测试仪,协议转换器,示意图如图8所示。JDSU ANT-5手持型SDH/PDH传输分析仪,内置所有必要的接口:从T1Bantam、E1平衡与E1非平衡,到STM-16/OC48光接口;测试速率从1.544 Mb/s~2.5 Gb/s;大屏幕、简单图形化界面、中文菜单,易于使用。

首先进行时隙分配设置,将1到15时隙分配给V.35接口,17到30时隙分配给RS 449接口,31时隙分配给RS 232接口。由JDSU ANT-5 SDH接入测试仪发出的2 MHz信号,进入协议转换器,然后分别将V.35,RS 449,RS 232接口环回,再将输出的E1信号接入测试仪,在测试仪中测试环回信号的各种特性。

4.2 测试结果

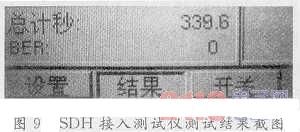

依照上述测试平台进行协议转换器功能测试,测试结果显示,误码率为0,说明协议转换器功能正常。JDSU ANT-5 SDH接入测试仪测试截图如图9所示。其中BER为误码率。

5 结语

本文提出了一种多路接口与E1的协议转换设计方法,并具体介绍了时隙分配及调度、空时隙处理等技术难点。通过实现V.35,RS449,RS 232三路接口与E1的协议转换,证明该方案是可行的。另外,本设计具有良好的扩展性,可以方便的根据具体应用添加或去除接口,也可以在本设计的基础上进行二次开发,完成更多的功能。

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- TM1300 PCI-XIO口的UART和USB接口设计(01-17)

- PC机扩展RS-232接口(01-25)

- LVDS接口电路及设计(01-26)

- 基于RTL8019AS的串口与以太网接口转换器(04-29)

- 串行及并行A/D转换器在高速数据采集中的采样差别性分析(05-19)