如何改善高速ADC时钟信号

您在使用一个高速模数转换器(ADC)时,总是期望性能能够达到产品说明书载明的信噪比(SNR)值,这是很正常的事情。您在测试ADC的SNR时,您可能会连接一个低抖动时钟器件到转换器的时钟输入引脚,并施加一个适度低噪的输入信号。如果您并未从您的转换器获得SNR产品说明书标称性能,则说明存在一些噪声误差源。如果您确信您拥有低噪声输入信号和一种较好的布局,则您的输入信号频率以及来自您时钟器件抖动的组合可能就是问题所在。您会发现"低抖动"时钟器件适合于大多数ADC应用。但是,如果ADC的输入频率信号和转换器的SNR较高,则您可能就需要改善您的时钟电路。

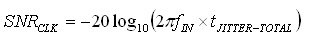

低抖动时钟器件充其量有宣称的1微微秒抖动规范,或者您也可以从一个FPGA生成同样较差的时钟信号。这会使得高速ADC产生SNR误差问题包括ADC量化噪声、差分非线性(DNL)效应、有效转换器内部输入噪声和抖动。利用方程式1中的公式,您可以确定抖动是否有问题,公式给出了外部时钟和纯ADC抖动产生的ADC SNR误差。

方程式1

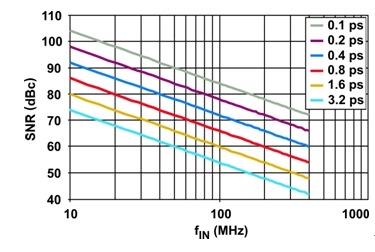

在该方程式中,fIN为转换器的输入信号频率。另外,tJITTER-TOTAL为时钟信号和ADC时钟输入电路的rms抖动。请注意,fIN并非时钟频率(fCLK)。外部时钟器件到ADC的1微微秒抖动适合于一些而不是所有高速ADC应用,如图1所示。

图1:抖动产生的SNR为输入信号的函数。

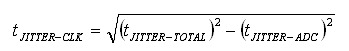

方程式1让您能够计算出特定ADC的要求时钟抖动估计值。例如,一个70dB SNR的ADC,输入信号为100MHz,您可以计算得到tJITTER_TOTAL的值为503微微秒。如果输入ADC孔径抖动为150微微秒,则由方程式2可得到一个较高的外部时钟抖动要求估计值。

方程式2

在方程式2中,tJITTER-CLK为注入ADC时钟的抖动,而tJITTER-ADC为ADC的孔径抖动、时钟振幅和斜率。继续我们的估算,我们让tJITTER-ADC只与ADC的150微微秒内部抖动相等,并忽略时钟振幅和斜率的影响。利用方程式2,tJITTER-CLK的高估值为480微微秒。

在本文中,我们只初步研究了改善高速ADC时钟信号背后存在的一些问题。我们需要更多地关注时钟振幅和斜率,因为它们影响系统抖动。另外,我们还需要知道如何实施低抖动时钟电路的硬件部分。

在本文介绍的第二种时钟设计之中,您需要认真关注几件事情。时钟抖动在ADC输入频率和实际时钟抖动方面影响ADC的SNR性能。另外,不要总是相信时钟器件厂商!在您转向产品以前,请使用ADC厂商提供的评估板来测试您的时钟源。您会对最终结果更为欣喜。

- 高速差分ADC驱动放大器AD8137及其应用(01-17)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 一种高速低压低静态功耗欠压锁定电路(03-13)

- 高速串行接口特征与应用(05-20)

- 高速数字电路电源系统的电磁兼容研究(11-20)

- 数字式超声波探伤仪中高速数据采集模块设计(04-04)