基于TLV1562的四通道高速实时数据采集系统的设计

时间:01-09

来源:EDN

点击:

1 引言

在雷达杂波对消器设计时,传统的方法是采用中频对消,即杂波的抑制在中频上实现。早期的中频对消器常采用SAW(声表面波)和CCD(电荷耦合器件)等模拟延时线。由于数字信号处理所具有的突出优点,尤其是数字集成电路的发展以及可编程逻辑器件功能的日益强大,使得数字式矢量对消器成为当前及今后的主要工作模式。而对雷达信号的采集与处理成为最为关键的环节,在设计中笔者选择了精度为10位的高速低功耗可重配置TLV1562,在较低成本下实现了多通道数据采集处理 。

2 系统设计与实现

2.1系统总体设计

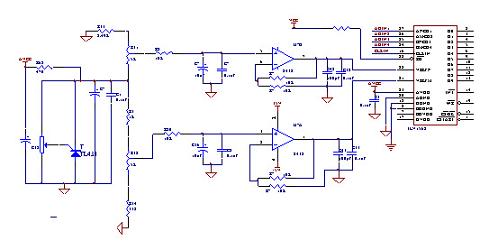

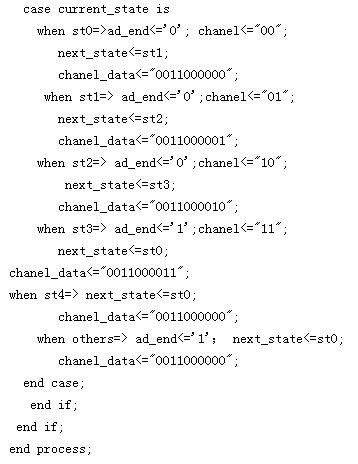

系统设计框图如图1所示,以TLV1562为核心的前端采集系统是整个系统的一部分。整个系统由信号调理、信号采样、高速信号处理(数字对消)以及波形回放等组成。信号调理电路是对经相干检波送来的信号进行压缩调整以满足TLV1562的采样电平;信号采样是完成模拟信号的数字化(由TLV1562完成);高速数字信号处理是在CPLD内完成数字式对消算法;由AD7533构成的波形回放部分是将对消处理过信号送到显示屏显示[3.4.5]

在雷达杂波对消器设计时,传统的方法是采用中频对消,即杂波的抑制在中频上实现。早期的中频对消器常采用SAW(声表面波)和CCD(电荷耦合器件)等模拟延时线。由于数字信号处理所具有的突出优点,尤其是数字集成电路的发展以及可编程逻辑器件功能的日益强大,使得数字式矢量对消器成为当前及今后的主要工作模式。而对雷达信号的采集与处理成为最为关键的环节,在设计中笔者选择了精度为10位的高速低功耗可重配置TLV1562,在较低成本下实现了多通道数据采集处理 。

2 系统设计与实现

2.1系统总体设计

系统设计框图如图1所示,以TLV1562为核心的前端采集系统是整个系统的一部分。整个系统由信号调理、信号采样、高速信号处理(数字对消)以及波形回放等组成。信号调理电路是对经相干检波送来的信号进行压缩调整以满足TLV1562的采样电平;信号采样是完成模拟信号的数字化(由TLV1562完成);高速数字信号处理是在CPLD内完成数字式对消算法;由AD7533构成的波形回放部分是将对消处理过信号送到显示屏显示[3.4.5]

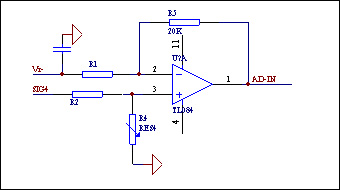

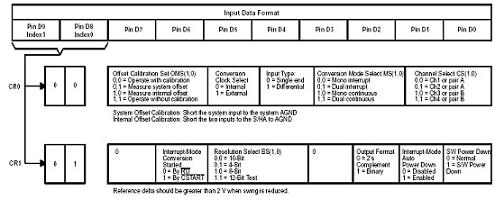

图1 雷达对消器系统总框图 2.2信号调理电路与A/D参考基准源的设计 由于对于规定的电源电压AVDD,TLV1562的模拟输入信号的范围为0.8~(AVDD-1.9伏),所以必须要对相干检波出来的模拟信号进行处理,使其满足要求。设计中,采用了如图2所示的调理电路,R4用来调整输入信号SIG4的幅度范围,Vr-是由TL431调整出来的一个基准电压,用来控制信号的直流电压[3]。

|

- 基于TLV1562的四通道高速实时数据采集系统(12-31)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 毫欧姆电阻在汽车电子系统中的应用(05-11)

- 24位高精度模数转换器ADSl258的原理应用(11-28)

- 电子式互感器中数据采集系统误差补偿的设计与实现(01-01)

- 用于大型地震勘探网的高精度低功耗自检测数据采集系统(02-20)