基于AHB接口的高性能LCD控制器IP设计

时间:09-03

来源:电子工程专辑

点击:

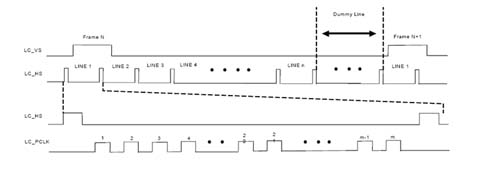

图3 STN在8位, 4位, 2位以及1位数据宽度的接口时序 LCD屏的宽度(PL)和高度(LF)寄存器里面定义了LCD面板的尺寸。LCD控制器将会以"LCD屏开始地址寄存器"(LCDImage0FrameBase)中的值为首地址来扫描显存,因此,被打上影音的区域将会最终显示在LCD面板上。 LCD虚拟页面宽度参数指定了最大显示页面宽度。通过修改LCDImage0FrameBase,可以使得真实显示的窗口大小和位置在虚拟页面边界的范围内变化。然后,对于编程人员来说,在软件设置定义显存扫描起地址的时候,是不能超多虚拟页面的高度和宽度,否则,屏幕上可能会有一些意想不到的景象。 这个IP在LCD屏的接口上还比一般的LCD控制器多了对串口RGB屏的支持,我们在FPGA开发板上就是使用AUO A036QN01串口RGB屏来验证。A036QN01的规格书上没有Dummy data(LCD Serial panel pixel Parameters: offset=0200H),但我们的design是有dummy data跟没有dummy data的可以支持的。 IP内部的接口时钟关系 以上就这个IP的原理与子模块作了充分的说明, 再接着介绍IP内部的接口时钟关系。 FTLCDC200包含了三个时钟域分别为HCLK, LC_SCALER_CLK以及LC_CLK。HCLK时钟使用于AHB接口而且这个时钟与AHB接口是一致的。AHB必须为SoC上的LCD控制器提供足够的带宽用以由帧缓存区捕获足够的数据。 LC_SCALER_CLK提供时钟给scaler模块同时对scaler模块也要足够快来处理数据。LC_CLK用于产生像素时钟。像素时钟(LC_PCLK是由LC_CLK产生并且除以1, 2, 3等等。 此外, 这三个时钟域必须按照下面的两个原则才能运行顺畅: ? 1. HCLK ≥ LC_SCALER_CLK ≥ LC_CLK (频率) ? 2. LC_SCALER ≥ HCLK/16 (频率) LC_CLK的频率变化依靠LCD屏的选择与使用。使用这个IP在频率上必须根据所选用的LCD屏的规格,下面两个例子介绍选择时钟频率的方法 |

AHB接口 LCD 控制器 FIFO SDRAM 相关文章:

- 为手持设备的被动式OLED显示器供电(11-25)

- LCD显示屏的器件选择和驱动电路设计(02-15)

- 基于DSP的液晶显示若干问题的探讨(06-02)

- LCD背光及对比度调节应用方案(-24V应用方案)(06-11)

- 世健基于Pearl的LCD电视解决方案(06-26)

- LCD驱动IC诸元趋势分析(11-05)