利用低成本高速放大器实现灵活的时钟缓冲器

时间:11-23

来源:EDN

点击:

与典型的时钟缓冲应用相比,消费类电子应用的工作频率较低,需求较少,采用低成本的高速运算放大器|0">放大器(~100MHz带宽)可以提供比传统的时钟缓冲器更具吸引力的替代方案。高速放大器比传统的时钟缓冲器更便宜,同时也能适应更多种类的设计配置。

对于低成本的时钟缓冲器而言,ADA4850 (-1/-2)、ADA4851 (-1/-2/-4)、ADA4853 (-1/-2/-3)和AD8061单电源运算放大器都是很好的选择。这些放大器都具有低电源电压、低电源电流、支持功耗敏感应用的省电模式,以及轨对轨输出等特性,可以实现宽动态范围。

与传统的时钟缓冲器相比,运算放大器的一个优点是具有灵活性。运算放大器可以将时钟脉冲进行缓冲、放大、失调、反向、相加、相减或滤波。它们提供高输入阻抗、低输入偏置电流、低电源电流、独立的省电模式(针对单个封装中的多个放大器)、低输出阻抗,以及低传播延迟。

当在时钟缓冲应用中使用运算放大器时,设计者必须认识到并遵循一些工作限制。以电压反馈型放大器的增益带宽积为例,当放大器电路的闭环增益增加时,它的带宽会降低,因此较大的增益意味着较小的带宽。将多个低增益放大器进行级联以达到较高的带宽,由此确保信号路径的总体增益和带宽。

单电源工作对于便携式电子设备来说是很重要的。根据定义,单电源运算放大器的输入共模范围包括负轨(地),大部分甚至比地还低200mV,但这并不表示输出电压的摆幅可以到地以下。典型轨对轨放大器的输出级采用共发射极配置。因此,输出电压和轨电压的最小差距是Vce(sat),其范围可以从数十毫伏到数百毫伏,具体取决于输出负载。

幸运的是,在这些应用中,输出电压的摆幅通常不需要总是达到地电压。但是,当输入太接近地时(大约100mv~200mv),输出级可能会达到饱和,导致失真以及较长的恢复时间。在直流耦合系统中,应该确保信号电压的低点高于200mV,或使用-200mV的负供电电压,这两种方法都可以避免输出级进入饱和状态。

放大器对裕量也有要求,也就是其电压的摆幅与正电源电压之间能够有多接近,因此还必须留意输入共模范围的高端。如果输入电压太高,输出电压会失真并被截断。ADA4850和ADA4851需要2.2V的裕量,AD8061需要1.8V的裕量,而ADA4853仅需要1.2V的裕量。

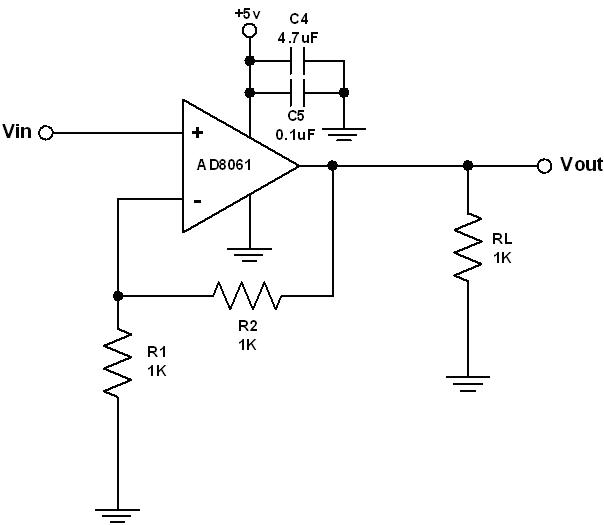

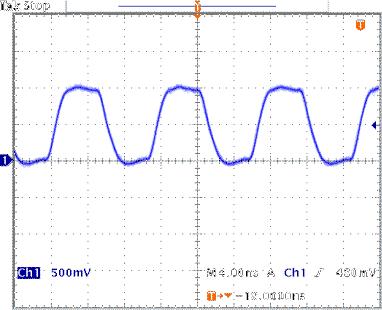

图1所示的是一个增益为2的单电源同向运算放大器时钟缓冲器,图2所示的是它的瞬态响应。按照配置,AD8061的上限约为33MHz,其2ns的传输延迟可与一些专用的时钟缓冲器相媲美。

对于低成本的时钟缓冲器而言,ADA4850 (-1/-2)、ADA4851 (-1/-2/-4)、ADA4853 (-1/-2/-3)和AD8061单电源运算放大器都是很好的选择。这些放大器都具有低电源电压、低电源电流、支持功耗敏感应用的省电模式,以及轨对轨输出等特性,可以实现宽动态范围。

与传统的时钟缓冲器相比,运算放大器的一个优点是具有灵活性。运算放大器可以将时钟脉冲进行缓冲、放大、失调、反向、相加、相减或滤波。它们提供高输入阻抗、低输入偏置电流、低电源电流、独立的省电模式(针对单个封装中的多个放大器)、低输出阻抗,以及低传播延迟。

当在时钟缓冲应用中使用运算放大器时,设计者必须认识到并遵循一些工作限制。以电压反馈型放大器的增益带宽积为例,当放大器电路的闭环增益增加时,它的带宽会降低,因此较大的增益意味着较小的带宽。将多个低增益放大器进行级联以达到较高的带宽,由此确保信号路径的总体增益和带宽。

单电源工作对于便携式电子设备来说是很重要的。根据定义,单电源运算放大器的输入共模范围包括负轨(地),大部分甚至比地还低200mV,但这并不表示输出电压的摆幅可以到地以下。典型轨对轨放大器的输出级采用共发射极配置。因此,输出电压和轨电压的最小差距是Vce(sat),其范围可以从数十毫伏到数百毫伏,具体取决于输出负载。

幸运的是,在这些应用中,输出电压的摆幅通常不需要总是达到地电压。但是,当输入太接近地时(大约100mv~200mv),输出级可能会达到饱和,导致失真以及较长的恢复时间。在直流耦合系统中,应该确保信号电压的低点高于200mV,或使用-200mV的负供电电压,这两种方法都可以避免输出级进入饱和状态。

放大器对裕量也有要求,也就是其电压的摆幅与正电源电压之间能够有多接近,因此还必须留意输入共模范围的高端。如果输入电压太高,输出电压会失真并被截断。ADA4850和ADA4851需要2.2V的裕量,AD8061需要1.8V的裕量,而ADA4853仅需要1.2V的裕量。

图1所示的是一个增益为2的单电源同向运算放大器时钟缓冲器,图2所示的是它的瞬态响应。按照配置,AD8061的上限约为33MHz,其2ns的传输延迟可与一些专用的时钟缓冲器相媲美。

|

图1. 同向运算放大器时钟缓冲器

|

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)

- 对数放大器的技术指标(11-26)

- 一种增大放大器增益的方法(11-28)

- 对数放大器的典型应用 (11-26)

- AGC中频放大器的设计 (11-29)