单端数字音频放大器设计中的考虑要素

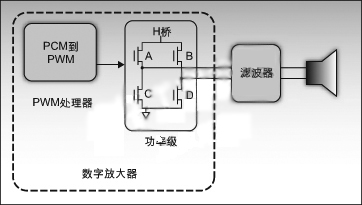

数字放大器一般具有两级架构,即在脉宽调制(PWM)处理器后接一个功率级(power stage),如图1所示。逻辑级PWM处理器接收的音频数据通常是IIS格式的。它执行音频处理并将脉冲码调制(PCM)数据转换为PWM数据。通过IIC总线控制PWM处理器,执行音量变化、音调控制或均衡等其它音频处理功能。许多PWM处理器还有另一个关键特性,即改变信号路由的能力(甚至可实时进行)。这种能力使设计人员可以灵活实现PCB布线,或使用户有能力将内容发送至不同扬声器。功率级接收3.3V PWM信号,然后将其转换为更高电压,并通过MOSFET H桥及二阶LC滤波器送至扬声器。

包含MOSFET H桥的功率级如图1所示。在这里,MOSFET用作开关将+V电压以正/负两个极向接到扬声器。对于将扬声器接在两个MOSFET半桥间的大多数立体声功率级而言,桥接负载(BTL)是常规架构。单端是指每个MOSFET半桥驱动一个扬声器。SE模式的声道数比BTL模式多一倍,但对给定的输出负载来说,每声道功率降低约25%。在SE模式,当PWM信号为"高"时,+V 电压正向加至扬声器;当PWM信号为"低"时,扬声器接地。

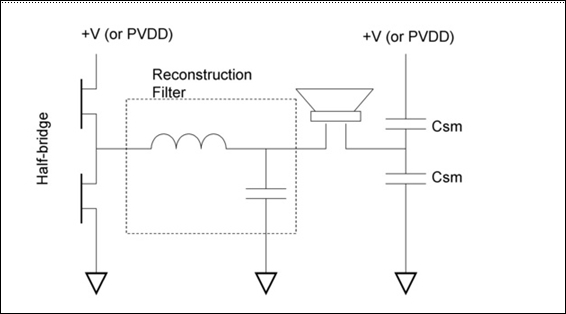

单端数字放大器的工作原理如图2所示,与线性音频放大器的单端工作相比没有太大差别。其主要区别在于,重构的滤波器(二阶LC滤波器)从PWM信号中滤出高频成分,保留基带音频信号。由于扬声器阻抗具有较大的电感成分,这相当于使一个高DC电压经过一个电感,并使电流以线性方式增加到一个很大的值,因而可能对扬声器造成损坏。

图1:具有H桥功率级的数字放大器数据通路。

图2:带DC阻断电容架构的单端数字放大器。

为此,可将一个大电容(DC阻断电容)放置在放大器和扬声器之间以滤除DC成分。不过该电容同时也会对较低音频成分造成衰减,并生成一个大约1/(2Rsp C)的3dB点,其中Rsp是扬声器的阻抗。为使更高的频带通过扬声器,可采用大电容器,但是这要以成本和PCB面积作为代价。

在先前讨论的单端架构中,音频信号以地为参考点。换言之,扬声器的一端接地。实现DC阻断的另一种方式是采用分割电容(split-cap )架构,其中音频信号以PVDD/2为参考点,见图3。从AC的角度看,当 Csm = Cb/2时,图2和图3没有区别。如果插入电容,Cs的等效串联电阻(ESR)是Cb的两倍,而音频和热性能没有变化。

图3:带分割电容架构的单端数字放大器

与阻断电容架构相比,分割模式架构的最大优点是增加了电源纹波抑制比(PSRR)。图4显示的是TI的TAS5086/5142评估模块(EVM)实际测量的PSRR。在该EVM中,TAS5142的功率级是单端架构。

图4:TAS5086/5142 EVM的单端PSRR性能

SE分割模式架构需要解决另两个设计问题。如先前提到的,重构滤波器后面的音频信号有值为PVDD/2的DC成分。若Cs是理想的,则(Cs和Cb)都将被充电至PVDD/2,且没有DC成分通过扬声器。但是由于两个电容都不理想且都有容差,所以DC电压不会等于PVDD/2。因此,当音频信号最初被加至扬声器时,将有DC电压流经扬声器,所以在上电时会听到噼啪的噪声。由于分割电容以时间常数为RC的固定时长充电,所以会产生另一个相关问题。只要MOSFET不在分割电容完成充完之前切换,就不会引发这些问题。但实际上这样做很困难,因而会产生长的噼啪噪音。

有一种方案可解决上述两个问题,即能将电压快速充至PVDD/2的半桥功率级,例如TAS5186A。该方案具有50%的占空比,DC电压输出是PVDD/2,且分割电容可被快速、准确地充电。另一个快速充电分割电容的方法是利用运放。在没有专用半桥时,采用运放是一种行之有效的办法。

在实际应用中,单端放大器音频性能指标(包括开机噪音、信噪比、PSRR和THD+N等)都相当理想,只比BTL的音频性能稍显逊色。

- 可自动关断的扬声器放大器,有效节省手机功耗(05-05)

- 陶瓷扬声器系统的放大器设计的解决方案(02-01)

- 扬声器系统的技术特性分析(11-23)

- BTL功率放大电路工作原理(12-14)

- 损坏扬声器的各种电气和物理效应及其保护方法(02-09)

- 新型平板扬声器的设计与实现(04-10)