基于NI-PXI的下一代超高速无线局域网原型系统设计

对其原型机进行开发验证,这对新一代Wi-Fi技术及5G技术的研究具有重要意义。

2、设计目标

本文旨在NI-PXI平台上实现一个基于IEEE802.11ac标准的系统原型机。该系统设计的参数指标如下所示:

1)系统基于IEEE 802.11ac协议;2)系统运行在2.4GHz/5GHz频段;

3)系统配置2个发射天线和2个接收天线;

4)系统的传输带宽达到20MHz;

5)调制可选方式:BPSK、QPSK、16QAM、64QAM、256QAM,并可根据接收信噪比实现自适应调制;

6)系统频谱效率:最高可达10 bit/s/Hz(在64QAM映射方式,码率为‘5/6’的条件下);

7)可以显示解调后的接收星座图;

8)可以实现视频的高质量传输。

原型机需要实现的IEEE 802.11ac协议物理层内容有:

1)发射端:BCC编码、流解析、调制、插入导频、加CP、IFFT;2)接收端:同步、去CP、FFT、信道估计与均衡、去导频、解调、逆流解析、维特比译码。

3、基于NI的802.11ac超高速无线局域网原型机

3.1、概述

该项目需要达到百兆数量级的数据传输速率,因而需求高速率的数据处理,在硬件实现中,我们选择了运用高性能FPGA来达到高速率的要求,然而开发这样一个系统需要我们很好的掌握VHDL或者Verilog HDL语言。同时,该项目还涉及了射频方面,这对我们来说也是一个巨大的困难,我们只希望将重点放在802.11ac协议的基带设计上,NI的LabVIEW软件及它的硬件平台对我们来说是一个福音,解决了我们的所有烦恼,让我们能专注于我们想专注的事,极大的缩短了我们的开发周期。

在下文中,我们将具体描述基于NI的802.11ac超高速无线局域网原型机。

3.2、硬件平台

原型机的硬件设计是基于NI-PXI平台来进行的,其硬件实物图如下图所示,两块FPGA板卡连接射频适配器置于机箱中,该平台主要包含机箱、控制器、FPGA模块、射频收发模块四个部分,各模块的性能及主要功能如下:

图1、系统硬件平台实物图

(1)NI PXIe-1082机箱:采用的该机箱包含4个混合插槽, 3个PXI Express插槽, 1个PXI Express系统定时插槽,每插槽高达1 GB/s的专用带宽和7 GB/s的系统带宽,与PXI、PXI Express、CompactPCI和CompactPCI Express模块兼容。机箱主要为控制器和各模块提供了电源、冷却以及PCI和PCI Express通信总线,此外还提供了一系列的I/O模块插槽类型、集成外设。

(2)NI PXIe-8115控制器:本系统采用NI PXI-8115作为控制器,位于机箱最左侧插槽。它是基于Intel Core i5-2510E处理器的高性能嵌入式控制器,适用于PXI系统。具有2.5 GHz基频、3.1 GHz(单核Turbo Boost模式)双核处理器和单通道1333 MHz DDR3内存,配有以太网、串口等标准设备,可自行选择操作系统,本设计选用了Windows系统。

(3)NI PXIe-7966R:针对无线局域网的数据传输,主要考虑数据的运算处理能力,选用FlexRIO模块。它包含两个主要部分:FPGA模块和提供高性能模拟和数字I/O的FlexRIO适配器模块。这些都可以被LabVIEW FPGA软件配置。

其中FPGA模块选用NI PXIe-7966R,它包含了一块Virtex-5 SX95T FPGA和512 MB的板载DDR2双端口RAM。这块FPGA包含了640 DSP slices,可以用它来实现信号处理,数字滤波,FFT逻辑等。另外,板载的双端口RAM理论吞吐量为3.2GB/s。PXIe-7966R支持高性能的P2P数据流传输。本系统中FPGA模块主要实现发射端、接收端的基带数据处理工作。

(4)NI 5791射频适配器: NI 5791是一款具有200 MHz到4.4 GHz连续频率覆盖范围的RF收发器,其中TX和RX端均具有100 MHz的瞬时带宽。它具有单级转向架构,在NI FlexRIO适配器模块的小巧组成结构中提供了超高的带宽。板载合成器(本地振荡器)用于设定采集和生成的中心频率,且可导出至其他模块,以实现多输入多输出(MIMO)同步。用户可直接访问NI FlexRIO FPGA模块的原始ADC和DAC数据。 此外,NI FlexRIO FPGA模块和PXI平台提供了一种实现通道扩展必需的ADC和DAC数据同步方法。

3.3、系统设计

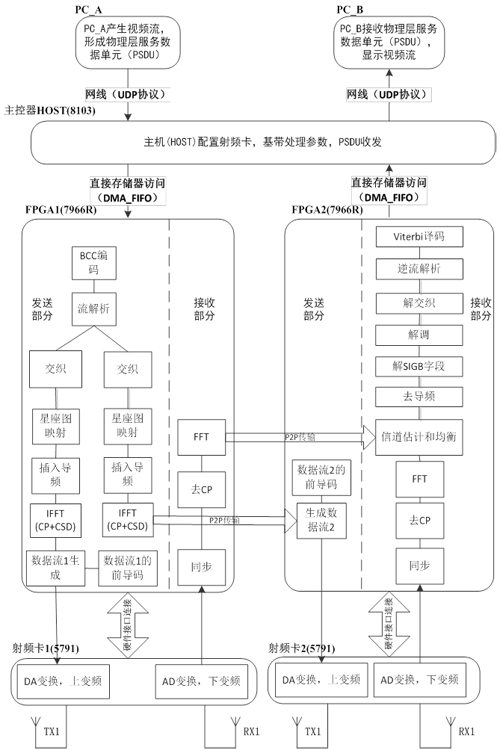

在这样一个实时高速传输系统里,系统架构设计尤为重要,良好的架构设计是系统正确运行的前提,也是提高系统性能的关键所在,本文原型机整个系统的结构框架如图2所示,系统设计主要分为PC端设计、HOST端设计、FPGA端设计三个部分,PC端设计基于C#语言实现视频的编解码等工作,而HOST端和FPGA端设计主要是基于LabVIEW编程实现,前者负责参数配置、数据传输等工作,后者负责实现IEEE 802.11ac协议的物理层模块。这三者之间也要进行数据同步。下文将对各个部分的设计进行详细的叙述。

图2、系统总体架构图

3.3.1、物理层数据通信

原型机物理层数据通信主要在PC端、HOST端

- Telefonica新智能测试平台整合M2M通信测量(02-21)

- 了解RF无线电广播(03-12)

- 了解RF仪器规格第一部(07-25)

- Mouser Electronics推出子网站专注于RFID和NFC技术 (08-06)

- PXI和LabVIEW应对下一代负载牵引测量速度(08-27)

- NI软件设计VST将功能主控权交回RF工程师手中(12-31)