Rapid IO---成就高速互连之美

逻辑层、传输层和物理层构成。最明显的一个特点就是Rapid IO采用了单一的公用传输层规范来相容、会聚不同的逻辑层和物理层,单一的逻辑层实体增强了Rapid IO的适应性。

物理层定义了串行和并行两个实体,得到广泛应用的只有串行方式,尤其是用在背板互连的场合,串行方式可以在两个连接器之间允许80-100cm的连线,单链路传输带宽可达10Gbps。目前Rapid IO的标准是Version1.3,在未来的Version2.0规范中定义了更高的传输速率,可以得到更高的传输带宽。

物理层:

Rapid IO规范中定义的最低层是物理层,最初定义的是并行总线,之后定义了串行总线,并线总线可以选择8位或16位的宽度,传输电平采用LVDS方式,时钟信息在一对单独的差分线上传送,不在数据流中编码,频率在250M-1.0G之间。相比串行总线而言,无多少优点可言,所以只是在最初有支持这种总线的芯片出现,目前几乎所有的物理层均采用了串行方式。

串行物理层定义了器件间的全双工串行链路,在每个方向上支持1个串行差分对称为1个通道(1x),或同时支持4个并行的串行差分对称为4通道(4x),接口的电气特性采用成熟的XAUI(10GbE Attachment Unit Interface)接口,编码方式采用的是8B/10B编码,对链路的管理,包括流量控制,包定界和错误报告等使用专用的8B/10B码(即K码),接收端从链路上提取时钟信息,无需独立的时钟线。每一个通道支持三种不同的传送波特率1.25G,2.5G,3.125G(与之相对应的数据速率分别是1.0G,2.0G,2.5Gbps)。

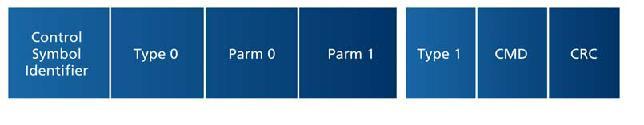

图:Control symbol 包的结构

Rapid IO是一种基于可靠传送的协议,每一个数据据包的传送均要求对端在物理层上响应一个控制符号包,此包是一个4个字节的数据包,表明了数据包的传送状态,数据包是否被对方接方,还是要求重新发送或是包未被接收。发送方和接收方均可以使用控制符号包来获得对方的状态。

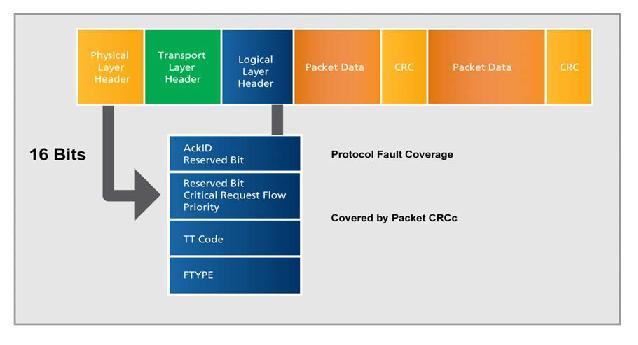

图:Rapid IO包结构及物理层组成

Ack ID被接收方用作发送响应包的ID号,表明此包是否被接收端接收,或是需要重传。Rapid IO协议定义了两个bit位用于表示包的优先级,所以共有4个优先等级,0是最低的,3是最高的,优先级高的包将被交换器优先传送。

每一个数据包都会被物理层附加上一个或两个16bit的CRC字段,用于接收方判断接收到的数据包的完整性,小于80个字节的数据包只有一个CRC,大于80个字节的数据包除了在第80个字节后有第一个CRC字段后,还会在包的末尾再加上一个CRC字段,实现数据包的检错,自动纠错和自动重传的功能,保证数据包被对端完整正确的接收。第一个CRC字段可用于对大数据包包头的验证,这样就可以在整个数据包被接收下来之前就可以进行对数据包的处理,交换器的直通模式就是利用了这个特性,这样可以有效减少传送时延。ACKID并不包括在CRC的计算范围内,这几个bit位在计算CRC时用0代替,这样就保证了在每一个链路上CRC无须被重新计算,当然如果HOP_COUNT字节有变化时,CRC还是需要重新计算的。

传输层:

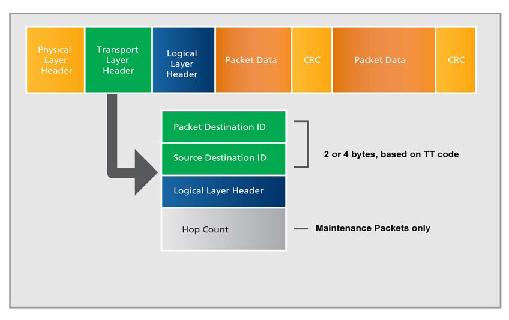

Rapid IO的第二层是传输层,实现Rapid IO数据包的路由、传送。所有的逻辑层协议均使用单一的传输层实体来实现,这样无论逻辑层怎么变化,或是采用何种方式来封装应用,都可以用单一的传输层实体来实现,即使有新的逻辑层规范出现,也可以用这个单一的传输层来实现。

Rapid IO的路由和交换是通过每个终端设备的ID号来实现的。每一个终端都会分配一个唯一的ID号,当一个终端发出一个数据包时,在它的包头中包含有目的终端的ID号和发送源端的ID号。每一个交换器在它的每一个端口上都有一个交换路由表,根据此表就可以决定此数据包由那一个端口送出。每个端口的路由表需要在系统初始化时进行配置,这与以太网相比,显得不是非常的灵活和智能,但正是如此,使得系统的路由实现变得非常简单。同样对于组播功能的实现也变得简单,只是由单一的传输层就可以实现了。

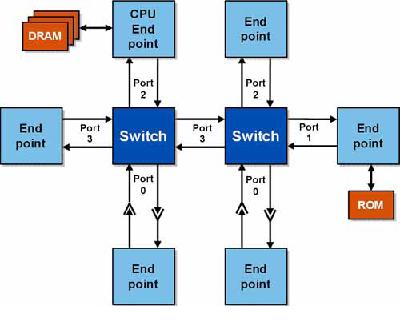

Rapid IO系统构成如左图,包括两类器件,一个是终端,产生数据包和接收数据包;另一类是交换器,实现数据包在各个端点间的路由和传送,且不对数据包做解释。

Rapid IO的传输层包头中的另一个字节是HOP_COUNT,是用来实现终端对交换器的初始化和路由配置,Rapid IO交换器的配置可以用任一个与之相连的终端进行配置,当交换器收到一个数据包时,它会首先判断收到包的HOP_COUNT值,如果此值是0则由此交换器终结此数据包,交换器利用此数据包的数据进行读写操作;如果此值不是0

- 串行RapidIO交换器的应用优势(11-25)

- 提高FPGA处理总线性能的RapidIO节点设计(05-22)

- 现场总线CANbus与RS-485之间透明转换的实现(01-26)

- PCI总线数据输出板驱动程序的开发(05-16)

- 采用PCI9052的ATM数据采集卡的接口电路设计(05-27)

- SJTAG技术在ATCA体系的应用(06-30)