无外接电阻的2倍增益采样与保持放大器

当你需要同时采样一个信号并放大时,可以将一个增益为1的通用采样与保持放大器与一个电压增益为1的放大器作级联。除一些特殊情况以外,这样的一款放大器都有两只外接电阻(参考文献1)。这些电阻即使在采样保持放大器的稳定状态下也会耗散功率。在单片IC中,电阻的功耗以及发热还不是外接电阻的唯一缺点。在一个硅片中集成精密电阻需要更多的工艺步骤,因为这类电阻都是薄膜NiCr(镍铬)或SiCr(硅铬)元件。制造商用激光修整这些电阻,以获得严格的容差值,从而导致IC的高成本。由于这些电阻占用的芯片面积大于标准信号处理晶体管,因此芯片面积一定更大,进一步增加了最终成本。无疑单片IC的设计者要尽量避免使用精密电阻。

如果一个采样保持放大器需要的电压增益为整数(多数情况下是这样),可以用一种替代方法增加输出信号的幅度。对电压增益G,电路可以同时跟踪临时对地跟踪电容的输入电压VIN。随后,在跟随中产生一个中断,并取消其中G-1个电容的对地基准。同时,跟踪电容逐个堆叠起来。堆叠后的电压是所有这些电容电压的总和,因此得到总值为GVIN。当采样指令发出时,常数电压GVIN保存在第G+1个对地存储电容中。

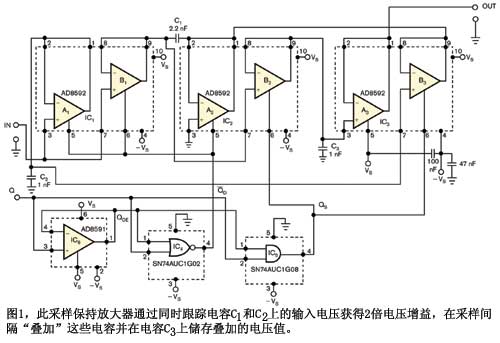

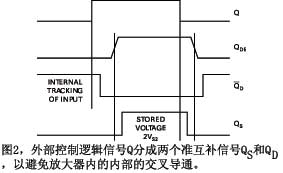

图1为一个电压增益为2的采样保持放大器实例。电压跟随器用关断功能控制着电容C1、C2和C3上的电势。设计采用Analog Devices公司的AD8592双运放,因为它们在关断模式的输出泄漏电流可以低至10pA(参考文献2)。采样保持放大器的运行可以看时序图(图2)。外部逻辑控制信号QS为低电平,而电容C1和C2同时跟踪其输入端电压。跟随器A1、B1和A2的关断输入捆绑在一起。当QD为高电平时,它们工作,因此输入电压出现在A1和B1的输出端,而在A2的输出端没有电压。在QD从高到低转变后,每个受控跟随器后的空槽关闭。当Q为高电平时,B3和B2导通。因此,C2上的电压出现在B3的输出端,输入电压的电势出现在C1的较低结点上(IC2的第2脚)。由于C1的电压与输入电压和输出电压相等,B2跟随器为2VIN。因此电容C3充电到电压2VIN。在QS的高至低过渡后,接下来是另一个空槽,以防止电路中的任何交叉导通。在QS下一次从高至低转变时,重复这个步骤。

A3跟随器用作一个阻抗转换器,输出C3上的电压。单个NOR和AND门与作为延迟线路的运放IC6一起修正单一的外部逻辑控制信号,以建立正确时序的内部逻辑信号QD和QS。

对于噪声分析,假定每个跟随器的噪声特性都是相同的,即每个跟随器输出电压的元件随机标准差为sA。在跟随周期结束时,C1与C2都充电到输入电压。VC2电压的标准差只对跟随器A1是sA。而VC1电压的标准差为?2 sA,因为C1通过两个串联的跟随器B1和A2充电。因此,电压VC1+VC2的标准差就是?3 sA。电压VC1+VC2在相同周期内通过两个级联跟随器B3和B2加在C3上。另外,VC3电压通过跟随器A3加在输出上。由于所有这些噪声源都相互独立,并且它们都是串联作用,输出电压的标准差为sOUT= ?6sA。增加整数增益至G值便得到?3 GsA。现在提出一个RSNR(相对信噪比),为增益G与输出端噪声相对增量之比,可得:

RSNR=

对于图1中的采样保持放大器,RSNR等于0.8165,意为电路的噪声特性略差于单个跟随器的情况。当增益为3时,RSNR值为1,而从增益4开始,RSNR为1.155,它随增加的增益而逐渐上升。结果是,当电压增益为4以上时,采样保持放大器的噪声特性要好于单跟随器的情况。

参考文献

1. tofka Marián, "Gain-of-two instrumentation amplifier uses no external resistors," EDN, Feb 15, 2007, pg 81.

2. "AD8592 Dual, CMOS Single Supply Rail-to-Rail Input/Output Operational Amplifier with ±250mA Output Current and a Power-Saving Shutdown Mode," Analog Devices Inc, 1999.

作者:Marin Stofka, Slovak University of Technology, Bratislava, Slovakia

保持放大器 相关文章:

- 无需外部电阻的反相取样保持放大器(10-20)

- 不外接电阻的双输入采样保持放大器(03-11)

- 不外接电阻的双输入采样保持放大器原理分析 (07-17)