谨防您下一个雄心勃勃的产品发布计划遭遇搁浅

在针对高价值 FPGA、ASIC 和微处理器的过压保护措施上少量投资,就能在可靠性、安全性和保修成本方面带来收益。

工业、航空航天和国防系统中常见之 24V 至 28V 中间总线与新式数字处理器之输入电源电压之间不断加大的差距带来了设计风险,有可能轻易导致系统故障、有毒烟雾甚至更加糟糕的火灾。相对较高的输入电压使得将电源电压保持在处理器的安全限值之内的难度越来越大,而且对产品的尺寸、生产费用、安全性和可靠性具有直接的影响。导致过压的此类风险包括但不限于:1) 中间电源总线上的输入浪涌过程;2) 开关稳压器 PFM / PWM 定时中的少许误差;3) 在制造过程中引入错误、水货或假冒电容器。尽管大多数公司均否认非法电子组件进入其组装线的可能性,但遗憾的是,我们在凌力尔特接到的客户电话、与其他公司同行开展的讨论、甚至美国参议院 2012 年 5 月发表的一篇报告均表明:黑市和假冒电子组件经常出现,即使在那些最富盛名的公司和最安全的应用中也不能幸免。

上面所列 3 种事件中的任何一种都可以引起超过负载额定值的输出电压摆幅,从而有可能导致昂贵的 FPGA、ASIC 或微处理器遭受永久性的损坏,在某些极端场合中甚至会造成起火燃烧。视损坏程度的不同,确定问题的根源或许相当具有挑战性,而且由此引起的高维修成本、客户生产效率的下降以及对您声誉的损害都会是极其令人沮丧的。

假如您的系统采用了中间电压总线,就应当考虑采取一种风险消减方案,以最大限度地降低成本并减少给客户带来的不便。传统的过压保护方案需采用熔丝,这不适合用来保护新式 FPGA、ASIC 及微处理器,特别是当上游电压轨的标称值为 24V 或 28V 时。响应时间变化多端而且准确度很差,以至于无法在此类高输入至输出电压比应用中保证保护功能的及时生效。此外,即使数字逻辑器件成功地得到保护,恢复过程也将十分漫长,最终造成的故障停机时间会让客户非常不满,因为在尝试系统重启之前必需通过人为干预来更换熔丝。

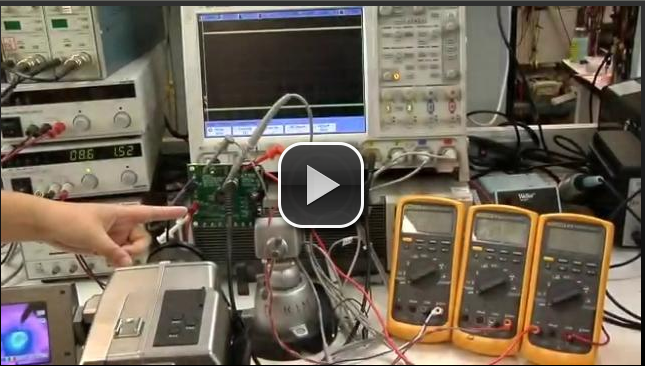

已经设计了一种新型解决方案,其将一个额定电压为 38V 的 10A DC/DC 开关稳压器与用于防范诸多故障 (包括输出过压) 的电路组合起来,以保护高价值的 FPGA、ASIC 或微处理器。针对负载上的过压状况,在工厂里对每个稳压器都进行了测试,并保证相关的保护电路可在故障发生后的 500ns 以内起作用,达到测试要求的器件方可提供给客户。此外,恢复过程快速且简单。只需对一个逻辑电平控制引脚进行电平变换即可恢复正常运作 (假设故障已被清除),否则保护功能电路将立即重新运行,表示存在某种更加严重的故障。现在,利用一款紧凑的表面贴装型器件就能为当今最先进的数字逻辑器件提供电源和保护。可观看以下技术视频短片中所做的演示。

- 严酷的汽车环境要求高性能电源转换(08-17)

- 管理多电压轨系统让数字电源管理变得简单(08-17)

- 电源监视器LTC4151对汽车应用的解决方案(08-10)

- 具USB OTG和过压保护的紧凑型电源管理器(08-17)

- 适合有源天线系统并内置保护和诊断功能的坚固、低噪声、稳定型电源(08-16)

- 并联充电器系统可从以往不可用的低电流电源收集功率(08-23)