基于精密逐次逼近型ADC基准电压源设计

31 ROUT 与频率

位于100 kHz以下,则输出阻抗低于0.1 Ω;而直流时则低于0.05 Ω,因此就我们1 MSPS下驱动AD7980的示例而言,它是不错的选择。在宽频率范围内保持低输出阻抗对于驱动基准电压输入而言非常重要。即便是较大的电容值,储能电容也永远无法消除基准电压输入端消耗的电流。电流纹波的频率成分是吞吐速率和输入信号带宽的函数。大储能电容处理与吞吐速率相关的高频电流,而基准电压缓冲器必须能够在最大输入信号频率(或储能电容阻抗变得足够低,可提供所需电流的频率)保持低阻抗。基准电压源数据手册中的典型曲线显示输出阻抗与频率的关系,选择基准电压源时应加以考虑。

AD8031就是一个很好的选择,它在容性负载大于10 µF时性能稳定。其它运算放大器(比如ADA4841)也会在大电容下稳定,因为它们主要驱动稳定的直流电平,但某些特定的运算放大器必须测试确定加载特性。在电容之前使用串联电阻以保持稳定并不是个好主意,因为这会增加输出阻抗。

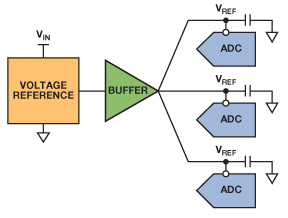

以一个基准电压源驱动多个ADC时,基准电压缓冲器非常有用,比如图6中显示的同步采样应用中的情形。

图6. 基准电压源电路驱动多个ADC

所有ADC基准电压输入都有各自的储能电容,尽可能靠近基准电压输入引脚放置。每条从基准电压输入出发的走线经路由后返回位于基准电压缓冲器输出端的星型连接,最大程度降低串扰效应。具有低输出阻抗和高输出电流能力的基准电压缓冲器可驱动许多ADC,具体取决于电流要求。请注意,缓冲器必须要能在额外电容下稳定,该额外电容与多个基准电压电容有关。

3 噪声和温度漂移

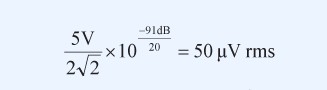

一旦确定了驱动能力,必须确保基准电压源电路的噪声不影响ADC性能。为了保持信噪比(SNR)和其它规格,必须将基准电压源噪声贡献限定为ADC噪声的一小部分(比较理想的是20%或更低)。AD7980集成5 V基准电压源,额定SNR为91 dB.转换为rms可得:

因此,基准电压源电路应具有不超过10 µV rms的噪声,以便最大程度减少对SNR造成的影响。基准电压源和运算放大器的噪声规格通常可分为两部分:低频噪声(1/f)和宽带噪声。结合这两部分可得到基准电压源电路的总噪声贡献。图7显示ADR431 2.5 V基准电压源的典型噪声与频率关系曲线图。

摘要:高分辨率、逐次逼近型ADC的整体精度取决于精度、稳定性和其基准电压源的驱动能力。ADC基准电压输入端的开关电容具有动态负载,因此基准电压源电路必须能够处理与时间和吞吐速率相关的电流。某些ADC片上集成基准电压源和基准电压源缓冲器,但这类器件在功耗或性能方面可能并非最佳--通常使用外部基准电压源电路才可达到最佳性能。本文探讨基准电压源电路设计中遇到的挑战和要求。

1 基准电压输入

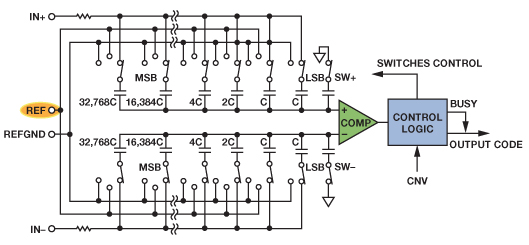

逐次逼近型ADC的简化原理图见图1.采样间隔期间,容性DAC连接至ADC输入,并且与输入电压成比例的电荷被存储在电容器中。转换开始后,DAC从输入端断开。转换算法逐个开关每一位至基准电压或地。电容上的电荷再分配可导致电流流入或流出基准电压源。动态电流负载是ADC吞吐速率和控制位检验的内部时钟的函数。最高有效位(MSB)保持大部分的电荷,需要大部分电流。

图1. 16位逐次接近型ADC原理简化图

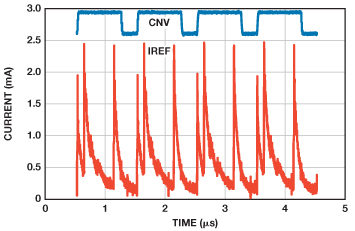

图2显示AD7980、16位、1 MSPS、PulSAR® 逐次逼近型ADC基准电压输入端的动态电流负载。通过观察基准电压源和基准电压引脚之间500 Ω电阻上的电压降,得出测量值。曲线显示电流尖峰高达2.5 mA,并且在整个转换期间分布着较小的尖峰。

图2. AD7980动态基准电流

若要支持该电流,同时保持基准电压的无噪声特性,需在尽可能靠近基准电压输入放置一个高数值、低ESR的储能电容,通常为10 µF或更大。较大的电容会进一步平滑电流负载,并降低基准电压源电路的负担,但极大的电容会产生稳定性问题。基准电压源必须要能提供灌满基准电容所需的平均电流,而不会导致基准电压下降过大。在ADC数据手册中,基准输入电流平均值通常在特定的吞吐速率下指定。例如,在AD7980数据手册中,将1 MSPS下5 V基准电压源的平均基准电流指定为330 µA典型值。两次转换之间不消耗电流,因此基准电流随吞吐速率成线性变化,在100 kSPS时降至33 µA.基准电压源--或基准电压缓冲器--在最高的目标频率下必须

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)