在异步SRAM中实现速度与功耗的完美平衡

时间:01-03

来源:3721RD

点击:

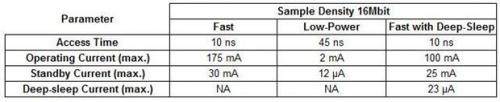

这些数字清楚地展示了与使用标准快速SRAM相比,使用"带深度睡眠模式"的SRAM的优势。在SRAM大部分时间都处于待机状态的应用中,该优势会更加明显。

我们来假设一个场景:某器件工作了一千个小时,SRAM的工作时间只占其中的20%.如果该SRAM是一款工作电压为3.3V的快速SRAM,那它的工作功耗就将为120瓦时(WH),待机功耗为80 WH.总功耗将为200 WH.现在,如果我们使用具有深度睡眠模式的快速SRAM,工作功耗依然是120 WH,但待机功耗则锐减至0.06 WH.总功耗大约为121 WH.因此在该具体应用中,深度睡眠选项可将功耗降低40%.然而在使用深度睡眠模式时(无论是MCU还是SRAM),需要考虑的一个因数是进入和退出深度睡眠模式所需的时间。如果这两个工作周期的时间间隔比SRAM进入和退出深度睡眠模式所用的时间还短,那该方法就不适合。

迄今为止,唯一推出支持片上电源管理的SRAM的公司是赛普拉斯半导体公司,该产品为PowerSnoozeTM.PowerSnooze SRAM采用54-TSOP和48-BGA等标准封装,与普通快速SRAM一样。为使用深度睡眠功能,该产品还提供了一个特殊引脚(DS),可将低电平有效切换至进入深度睡眠模式。标准快速SRAM上的同等引脚恰恰是无连接(NC)。因此只需极少的设计工作(只需连接一个额外的引脚),便可将标准快速SRAM升级为PowerSnooze SRAM.

- 基于μC/OS-II嵌入式系统的低功耗开发(07-08)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- AVR单片机介绍(07-09)

- 基于WinCE5.0的嵌入式设备休眠唤醒技术研究(09-27)

- DSP电源系统的低功耗设计(11-13)

- 基于DSP的低功耗接收机单边带解调方法(01-10)