分布式网络化视频监控系统的设计实现,系统框图、硬件原理

项目背景及可行性分析

1.项目名称、项目的主要内容及目前的进展情况

1)项目名称:分布式网络化视频监控系统

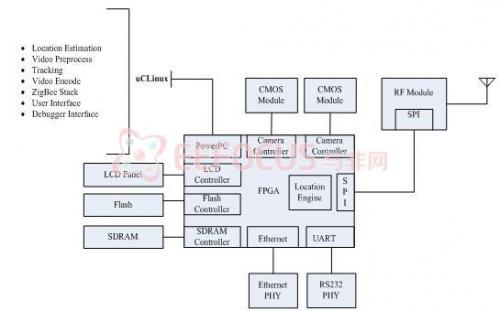

2)主要内容:构建以FPGA为核心的通信处理模块,内置一个32位处理器,加载uCLinux操作系统,驱动两个CMOS接口、一个SPI射频接口、一个以太网接口、一块液晶显示器;硬件加速定位、图像预处理、编码等算法;开发良好人机交互接口。

3)目前进展:目前已经完成需求说明,总体模块划分。自开发的无线射频模块已经完成。发射功率32级可编程,最大发射功率0dBm,接收灵敏度-85dBm,有效带宽200kpbs。

2. 项目关键技术及创新点的论述;

1)基于FPGA的嵌入式视频技术

2)分布式网络智能监控技术

3)基于ZigBee网络的定位技术

4)基于动态局部重配置技术的智能检测与视频检测模块复用技术,充分利用FPGA上的硬件资源。

传统视频监控系统单纯依赖提高CCD摄像机图象质量和大面积布置摄像机来获得高质量的全方位监控。但是此类系统需要昂贵的摄像机为终端,辅助良好的照明环境,建设和维护成本昂贵,能耗较高;同时需要架设很长的供电电缆和视频传输电缆将摄像机与监控中心相连,施工复杂,成本昂贵;监控中心多采取效率低下的人工监控和硬盘录像方式,智能化程度较低。

本项目所述系统采用ZigBee构建定位网络和数据网络,其中节点采用以高性能FPGA为核心,配置低功耗CMOS摄像头模组,实现移动物体的定位、跟踪和图象处理及传输功能。系统以智能检测技术确定运动物体所在的敏感区域,激活该区域内节点运行图象处理算法,提取运动物体的准确位置、行为状态,并将图象传输至监控中心。该系统具有以下创新点:

1)监控系统以定位、跟踪和传输三个层次,只针对运动物体进行计算,能有效配合传统监控系统,实现主动监控和智能监控;

2)所有部件采用低功耗电路和睡眠唤醒等软件功耗算法,可实现电池供电,安装、调试简单;

3)FPGA内集成32位处理器、视频接口、射频接口和其它数字接口,系统复杂度和成本有效降低;

4)采用FPGA硬件加速处理数字图象、无线通信协议,运算速度快;

5)基于动态局部重配置技术的智能检测与视频检测模块复用技术,充分利用FPGA上的硬件资源。

6)通信链路采用无线方式,安装简单,施工方便。

3. 技术成熟性和可靠性论述:

FPGA容量不断扩大,价格更加贴近大众,同时大量免费的IP库和开放源码使基于IP的SoC设计成为技术主流,加速了系统开发过程。以IEEE802.15.4为PHY和MAC层的ZigBee自2003年发布规范以来,得到了TI、Freescale和Microchip等联盟成员的大力支持,解决方案成熟并推向市场应用。CMOS技术在功耗、像素、帧率方面都取得突破,400万以上像素模块组已普遍应用。虽然现在系统整体上定位较高,但随着技术进步,在不远的将来价格将不会是系统大规模应用的主要限制因素。

项目实施方案

1.方案基本功能框图及描述

本方案总体结构如下图所示:

1)定位 分两个阶段: 相对节点定位--采用运动物体进入节点通信区域前后射频能量变化为特征确定运动物体的最临近节点,确定敏感区域。利用了运动物体对无线电波产生扰动的特性。节点附近的精确定位--利用CMOS摄像机监控区域小,针对简单二维画面,图像容易做背景过滤、运动物体提取处理。

2)跟踪 发挥网络覆盖密集特性,在定位基础上敏感区域附近节点相互协作,共享定位信息,直接利用各节点覆盖重叠的优势跟踪物体。

3)传输 传输定位信息和敏感区域图像信息,同时利用视频压缩算法,符合ZigBee带宽要求。

2.需要的开发平台

实现本方案所需要的基本功能、功能接口

构建以FPGA为核心的通信处理模块,要求内置一个32位处理器,加载uCLinux操作系统,驱动两个CMOS接口、一个SPI射频接口、一个以太网接口;支持ICAP,能实现动态重配置;含有多个DCM;可编程资源丰富,便于实现硬件加速定位、图像预处理、编码等算法;含有SRAM、DRAM和FLASH;开发良好人机交互接口。

所需要的目标FPGA开发平台,简述为什么需要此平台

目标平台为Virtex II Pro开发平台,主要是因为:本项目属于无线智能监测处理系统,需要硬件处理平台具有较高的处理速度和丰富的逻辑资源以实现无线协议、大量的数据处理以及智能检测算法和图象处理算法的硬件加速,而Virtex-II Pro XC2VP30含有3万个Logic cells,8个DCM,足以胜任本设计;本项目需要该开发板中的ICAP协助重配置开发;另外板上FPGA内含有两个PowerPC硬核,便于进行嵌入式软件开发和控制流设计,足以胜任复杂的无线网络协议、实时的图象的

ZigBee FPGA Virtex II 视频监控 相关文章:

- 浅析基于MG2455微处理器Zigbee的汽车无线黑匣子实现(08-29)

- 基于ZigBee的城市照明监控系统网关节点的软硬件设计(01-15)

- 基于RSSI测距的定位算法的研究(01-15)

- 基于GPRS和ZigBee的远程油阀控制系统(01-17)

- 基于ZigBee无线网络的嵌入式智能家居监控系统(03-18)

- 设计实例:森林火灾实时监测与预警系统(03-18)