ARM微处理器的编程模型之:数据类型

3.1 数据类型

3.1.1 ARM的基本数据类型

ARM采用的是32位架构,ARM的基本数据类型有以下3种。

· Byte:字节,8bit。

· Halfword:半字,16bit(半字必须于2字节边界对齐)。

· Word:字,32bit(字必须于4字节边界对齐)。

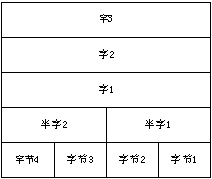

存储器可以看作是序号为0~232−1的线性字节阵列。图3.1所示为ARM存储器的组织结构。

图3.1 ARM存储器组织结构

图3.1所示为存储器的一小片区域,其中每一个字节都有惟一的地址。字节可以占用任一位置,图中给出了几个例子。长度为1个字的数据项占用一组4字节的位置,该位置开始于4的倍数的字节地址(地址最末两位为00)。图3.1中包含了3个这样的例子。半字占有两个字节的位置,该位置开始于偶数字节地址(地址最末一位为0)。

| | 注意 | ① ARM系统结构v4以上版本支持以上3种数据类型,v4以前版本仅支持字节和字。 ② 当将这些数据类型中的任意一种声明成unsigned类型时,N位数据值表示范围为0~2n−1的非负数,通常使用二进制格式。 ③ 当将这些数据类型的任意一种声明成signed类型时,N位数据值表示范围为−2n−1~2n−1−1的整数,使用二进制的补码格式。 ④ 所有数据类型指令的操作数都是字类型的,如"ADD r1,r0,#0x1"中的操作数"0x1"就是以字类型数据处理的。 ⑤ Load/Store数据传输指令可以从存储器存取传输数据,这些数据可以是字节、半字、字。加载时自动进行字节或半字的零扩展或符号扩展。对应的指令分别为LDR/BSTRB(字节操作)、LDRH/STRH(半字操作)、LDR/STR(字操作)。详见后面的指令参考。 ⑥ ARM指令编译后是4个字节(与字边界对齐)。Thumb指令编译后是2个字节(与半字边界对齐)。 |

3.1.2 浮点数据类型

浮点运算使用在ARM硬件指令集中未定义的数据类型。

尽管如此,但ARM公司在协处理器指令空间定义了一系列浮点指令。通常这些指令全部可以通过未定义指令异常(此异常收集所有硬件协处理器不接受的协处理器指令)在软件中实现,但是其中的一小部分也可以由浮点运算协处理器FPA10以硬件方式实现。

另外,ARM公司还提供了用C语言编写的浮点库作为ARM浮点指令集的替代方法(Thumb代码只能使用浮点指令集)。该库支持IEEE标准的单精度和双精度格式。C编译器有一个关键字标志来选择这个历程。它产生的代码与软件仿真(通过避免中断、译码和浮点指令仿真)相比既快又紧凑。

3.1.3 存储器大/小端

从软件角度看,内存相对于一个大的字节数组,其中每个数组元素(字节)都是可寻址的。

ARM支持大端模式(big-endian)和小端模式(little-endian)两种内存模式。

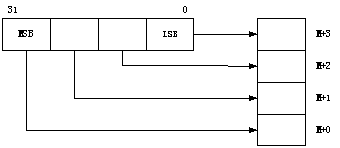

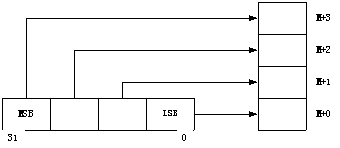

图3.2和图3.3分别显示了内存的大端模式和小端模式。

图3.2 大端模式

图3.3 小端模式

下面的例子显示了使用内存大/小端(big/little endian)的存取格式。

【例3.1】

程序执行前:

r0=0x11223344

执行指令:

r1=0x100

STR r0,[r1]

LDRB r2,[r1]

执行后:

小端模式下:r2=0x44

大端模式下:r2=0x11

上面的例子向我们提示了一个潜在的编程隐患。在大端模式下,一个字的高地址放的是数据的低位,而在小端模式下,数据的低位放在内存中的低地址。要小心对待存储器中一个字内字节的顺序。

微处理器 ARM 数据类型 Byte Halfword WORD 相关文章:

- 用8位微处理器实现数字低通滤波器设计(05-15)

- 如何构造嵌入式Linux系统(05-23)

- 基于嵌入式Linux的便携式RFID信息采集与处理系统(07-01)

- SPARC微处理器综述(05-29)

- Motorola32位嵌入式微处理器MPC860的开发应用(06-02)

- 基于ARM和uClinux的家庭网关系统(09-14)