基于DSP的数字音频均衡器设计

均衡器是一种可以分别凋节各种频率成分电信号放大龟的电子设备,通过调节音频均衡器的参数,可以补偿扬声器和声场的缺陷,起到补偿和修饰各种声源的作用。

分立器件与运放构建的模拟电感音频均衡器,因受分立器件本身性能的影响,存在许多不利因素,使该音频均衡器在竞争中处于劣势。提出了在ADSP-BF533硬件系统上设计数字音频均衡器的方法。谱分析算法采用FFT,其程序设计可以调用DSP的实时信号处理库函数。均衡器的设计算法采用FIR滤波器的设计方法,FIR滤波器具有严格的线性相位,均衡后的音频不会产生相位失真。系统相对于模拟音频均衡器有较大的优越性,设计灵活、运算精度高、处理速度快、满足实时信号处理的要求。

1 数字音频均衡器的硬件设计

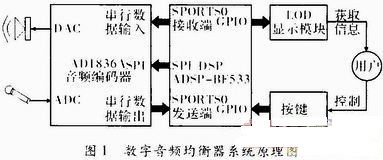

硬件平台以ADSP-BF533(DSP)作为数字信号处理核心,AD1836A作为音频采集和播放单元,LCD显示模块和按键实现人界交互。系统原理如图1所示。

模拟音频信号经AD1836A模数转换,南DSP数字均衡后再传送给AD1836A进行数模转换,以实现音频信号的均衡。用户可以通过LCD显示模块和按键来改变DSP中的软件处理流程或参数,完成对数字音频均衡器的控制。

1.1 主处理器ADSP-BF533

ADSP-BF533处理器是ADSP Blackfin系列的成员,其结构采用了微信号结构(Micro Signal Architecture),具备简洁的RISC指令集结构。内部指令处理采用流水线技术,并集成乘累加单元(MAC)和算术逻辑单元(ALU),其最高核频率可达600 MHz。

BF533集成了丰富的外设接口,在数字音频均衡器中使用SPORT0完成数字音频的数据传输,使用SPI来配置AD1836A的工作模式,并用可编程标志(PF)与LCD、按键进行连接。

1.2 音频编码器AD1836A

AD1836A是一个高性能的单片编码器,能够提供3个立体声的DAC和2个立体声的ADC。DSP通过SPI将AD1836A配置采样率为48 kHz,数据字宽为24位的音频编码器,并通过SPORT和AD1836A进行数据的传输,其串行数据端口可以采用流行的I2S串行模式。

1.3 LCD显示模块设计

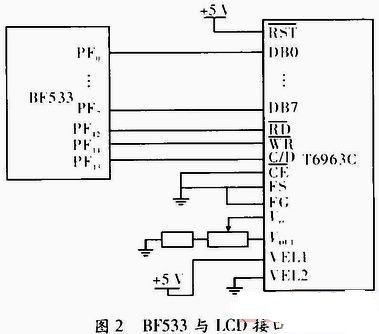

LCD选用MSP-G240128DYSY的点阵式液晶显示模块,该液晶显示模块的驱动控制系统由液晶显示控制器T6963C及其外围电路、行驱动器组、列驱动器组和液晶驱动偏电压电路组成。BF533通过PF接口实现对T6963C8位数据总线和控制线的读写。其中使用PF0~PF7为数据线,PF12~PF14为控制线,图2给出了BF533和LCD的接口方式。

2 数字音频均衡器的软件设计

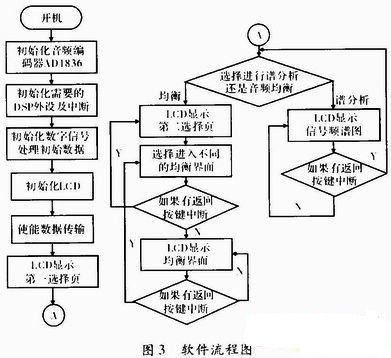

软件流程如图3所示,首先对BF533进行一系列的初始化,将系统设置在确定的工作状态下。初始化完毕用户通过按键选择LCD的菜单项控制音频信号处理。

2.1 音频信号的谱分析算法

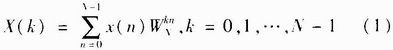

在音频信号处理中加入谱分析可以更直观地看出对不同频段的增益调节效果,方便了调节和分析。频谱特性曲线可以通过离散傅里叶变换得到,如式(1)所示。

式中,x(n)为音频信号采样序列;为旋转因子;N为DFT变换区间长度;X(k)可以用来描述其音频信号的频谱。

实际操作中AD1836A每次通过SPORT0,将4个24位的采样数据送入SPORT0接收缓冲区,并产生一次接收中断,在中断服务程序中接收的数据被送入设定的缓冲区中,当接收计数器达到N时,对采样数据进行FFT,计算出的幅频特性曲线实时显示在LCD上。

2.2 音频信号的均衡器算法

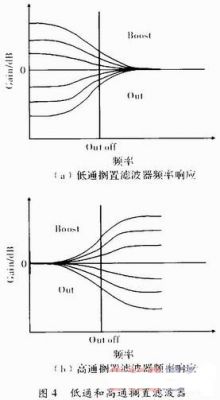

均衡器的作用是对信号的某段特定频率成分进行推进或衰减。只调节低频或高频增益的均衡器,是由搁置滤波器(Shelving Filter)控制,低频调节由低通搁置滤波器实现,高频调节由高通搁置滤波器实现,其频率响应如图4所示。

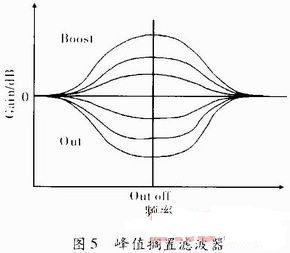

在大多数应用中,低通和高通滤波器是尽量对频谱的一部分完全删除。但搁置滤波器仅仅是对频谱的一部分进行推进或衰减,而留下剩余部分不受影响,此时就需要设计一个峰值滤波器或带通滤波器,其频率响应如图5所示。

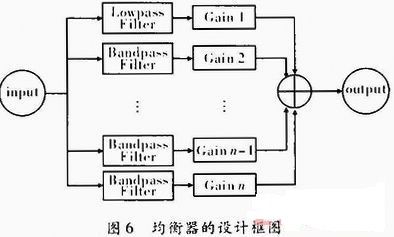

这3种滤波器组成了最简单的均衡系统,本系统是要设计一个图示均衡器,其操作简单便于控制,由一系列的固定中心频率的峰值滤波器组成,可以得出图示均衡器的设计框图如图6所示。

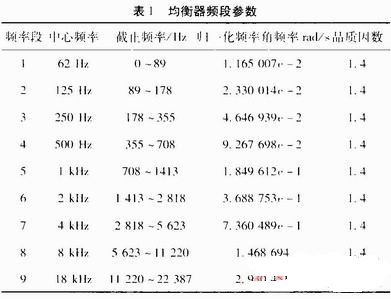

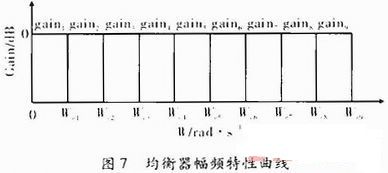

按照上述思路,实际上只需设计均衡器中的滤波器即可,根据线性系统的叠加性,以上的各个滤波器可以并联成一个系统函数,这个系统函数是要求线性相位,以满足不失真的还原出声音信号,而线性相位FIR数字滤波器正好满足上述条件。系统设计了一个9段的均衡器,将AD1836A初始化为采样率fs=48 kHz,定义归一化频率λ=f/fs,可以给出均衡器各个频率段的参数如表1所示。

设计理想滤波器传输函数,其幅频特性如图7所示,其中gain1~gain9是9个频率段的增益,每个频率段的增益可调范围是-12~12 dB。

由图可以看出均衡