基于DSP与SJA1000的CAN总线系统设计方案

时间:07-15

来源:3721RD

点击:

CPLD程序设计

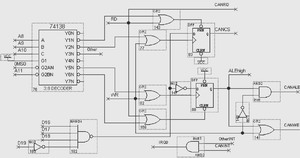

图4 CPLD的逻辑图

图4中,用74138进行译码,生成ALE、CS等信号。当执行指令6时,设置了外部空间的大小,在访问地址0x400000~0x4fffff时会使能MS0,74138的G2AN将有效。当地址A11"A8=0001,Y1N=0,CANCS的清零由DSP的RD控制,RD信号的低电平将使CANCS=0,指令11完成此功能。当地址A11"A8=0010,数据D19"D16=1000,则Y2N=0,DSP的WR信号的将使CANCS=1,指令14完成此功能;当地址A11"A8=0101,数据D19"D16=0111,则Y5N=0,DSP的WR信号沿将使ALEhigh=1,此时CANWE始终保持1,CANALE为WR取反,指令8完成此功能;当地址A11"A8=0110,则Y6N=0,RD信号的低电平将使ALEhigh=0,此时CANALE始终保持0,CANWE为WR,指令10完成此功能。

ADSP21062仅有3个外部中断,在挂多个外设时就显得资源紧张。图4中,低电平有效或下降沿有效的中断信号可以用与的关系连接到一个中断上,DSP在响应中断后,读相应的多个外设,判断是来自哪一个外设,这样就可以扩展更多的中断。

结语

SJA1000接口为地址/数据复用模式,DSP处理器通常为地址/数据总线分离的结构,本文提供了两种不同接口的思路和方法。测试表明,这种方法确实可行,传输效率高。

CAN总线 DSP SHARC SJA1000 接口设计 相关文章:

- 对TTCAN的分析(05-26)

- 嵌入式Win CE中CAN总线控制器的驱动设计与实现(05-01)

- μC/OS-II的多任务信息流与CAN总线驱动(07-11)

- 采用CAN总线实现DSP芯片程序的受控加载(11-08)

- 基于DSP的电动汽车CAN总线通讯技术设计(10-08)

- 基于DSP的CANopen通讯协议的实现(01-18)