嵌入式程序中的指令数据存储及读取设计

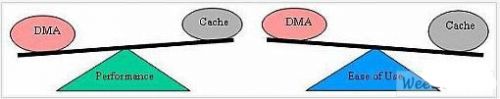

在当今的嵌入式多媒体应用中,系统控制(通常的MCU作用)和信号处理(通常的DSP作用)之间的交互性不断增强。现在推出的一种嵌入式媒体处理器能够同时处理MCU和DSP的任务,从而将那些熟悉用MCU方式进行应用开发的C程式师带入一个新的领域,其中对代码和资料流程的智慧管理会显着提高系统的性能。这对于採用"已经掌握"的编程方法和简单的使用指令高速缓冲记忆体(cache, 简称快取记忆体)和资料快取记忆体来管理这些资料流程的程式师很有吸引力。然而,对媒体处理器的高性能直接记忆体访问(DMA)能力应认真地考虑。因爲懂得在这些应用中对使用快取记忆体和DMA进行权衡将有助于更好地理解如何编程来优化系统。

记忆体结构--对记忆体管理的要求

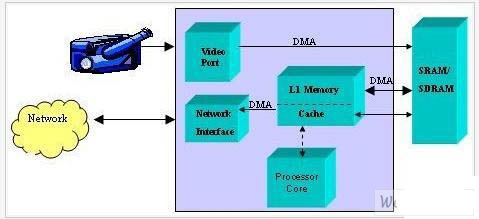

当今的媒体处理器具有分级的记忆体结构,用来平衡几种不同容量和性能等级的记忆体。通常,离核心处理器最近的记忆体(称爲"1级"或"L1"记忆体)以全时钟速率工作,通常支援单时钟周期指令的运行 了高效地利用记忆体匯流排的带宽,L1记忆体一般分爲指令段和资料段。通常,该记忆体被配置成SRAM或快取记忆体。对于那些许可权最高的应用,在一个单时钟周期内就能够访问片内SRAM。对于要求较长代码的系统,则可以提供附加的片内和片外记忆体--同时增加了等待时间。

这种层次结构本身作用有限 了适应仅配合低速外部记忆体的大部分应用,当今的高速处理器却以很低的速度降级使用 了提高性能,程式师可以人工地选择将关键代码移入或移出内部SRAM。另外,将资料快取记忆体和指令快取记忆体加入这种结构使程式师能够更方便地人工管理外部记忆体。快取记忆体减少了将指令和资料流程送入处理器内核的人工管理传送。这样程式师无需考虑如何把资料和指令流送入处理器内核,从而极大地简化了编程模式。

指令记忆体管理--快取记忆体还是DMA?

对嵌入式媒体处理器市场的快速调查表明,核心处理器的速度大于或等于600 MHz。尽管这种性能可以开闢许多新应用,但只有在从内部L1记忆体中读取代码时才能达到这种最高速度。当然,理想嵌入式处理器可以具有无限容量的L1记忆体,但这不切实际。因此,程式师在爲其实际系统优化记忆体和资料流程时,必须考虑几种可选方案以充分利用置于处理器内的L1记忆体。让我们来考虑一下其中的一些方案。

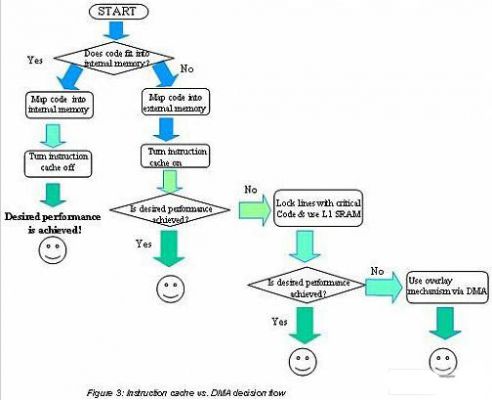

第一种方案同时也是最直接的方案,目标应用代码可以完全放入L1指令记忆体。对于这种情况,程式师只需将应用代码直接映射到该记忆体空间,无需特殊操作。这就是爲什麽包含MCU和DSP两种功能的媒体处理器必然在这种体系架构支援的代码密度方面具有独特优势的原因。

第二种方案,採用一种快取记忆体机构允许程式师访问更大容量、较低成本的外部记忆体。根据需要,这种快取记忆体可以作爲一种将代码自动送入L1指令记忆体的方法。这种方法的主要优点是程式师无需管理代码移入和移出快取记忆体。当执行线性代码时,这种方法达到最好的效果。当执行非线性代码时,快取记忆体线可能会被替换得太频繁,以致于不能提高即时性能。

指令快取记忆体实际上具有两个作用。第一,它以更有效率的方式从外部记忆体中预取指令。第二,由于快取记忆体一般使用某种"最近使用的指令"的演算法,所以那些用得最频繁的指令往往就被保持在快取记忆体中。这样做很有好处,因爲存在L1快取记忆体中的指令能够在一个单时钟周期内完成,就像指令在L1 SRAM中一样。也就是说,如果该代码一旦被取走,并且还没有被覆盖,即准备在下一个指令周期执行该代码。

大多数严格的即时程式师一般不相信这种快取记忆体能带来最佳的系统性能。他们的理由是如果一系列指令在需要执行的时候却没有在快取记忆体内,将导致影响性能。採用快取记忆体锁定机构能弥补这个问题。一旦将关键的指令装入快取记忆体,快取记忆体线就被锁住,因此指令不会被覆盖。这样,程式师就能够在快取记忆体中保持他们所需指令,并且使该快取记忆体机构管理次要指令。

最后一种方案,通过使用一个独立于处理器内核的DMA通道将代码移入或移出L1记忆体。当该处理器内核在记忆体的一个存储块运行时,该DMA将代码送入下一个存储块去执行。这种方案通常被称爲一种覆盖技术。

虽然通过DMA将覆盖代码送入L1指令记忆体可以比快取记忆体方式提供更多的关键指令,但其代价是要增加程式师的工作量。换句话,程式师需要预先安排一种覆盖代码的方法和恰当地配置DMA通道。对于一种能够做有价值的额外管理程式的详细计划,这种性能仍然会提高。

资料记忆体管理

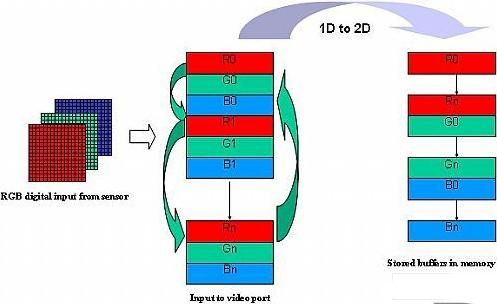

嵌入式媒体处理器的资料记忆体结构对于整个系统性能的重要性等同于指令时钟速度的重要性。因爲在多媒体应用中的任一时间经常会有多个资料传送任务同时进行,所以其匯流排结构必须支援内核和DMA对所有外部和内部记忆体块的访问。对DMA控制器和内核之间的冲突进行自动处理是非常关键的,否则性能将大大降低。首先要求在内核与DMA之间的建立DMA控制器,然后当要进行处理的资料已经准备时再应该回应中断。

处理器通常作爲其一项基本功能执行资料读取操作。虽然这通常是传送资料效率最低的机构,但它是最简单的编程方式。小容量、快速方便的记忆体有时可以用来作爲L1资料记忆体的一部分,但对于较大容量、片外缓冲器,如果内核要从外部记忆体读取所有资料,那麽访问时间就长得难以忍受。内核不仅要花掉多个时钟周期去取资料,而且它要花很多时间忙于读取资料。在多媒体和其他大量资料操作应用中,要不断地将大量资料存储移入或移出SDRAM,内核的读取资料操作是无法应付这种情况的。虽然内核的读取资料操作总是需要的,但爲了维持性能,一定要使用DMA或快取记忆体传送大量的资料。

- Linux嵌入式系统开发平台选型探讨(11-09)

- CDMA2000基带信号发生器的FPGA+DSP实现(05-29)

- DSP中DMA操作的无阻塞请求实现(06-18)

- DSP嵌入式视频监测(06-02)

- 基于VxWorks的系统故障快速恢复设计(01-12)

- 基于 DSP-dMAX 的嵌入式 FIFO 数据传输系统设计(04-11)