基于DSP的多路语音实时采集与压缩处理系统

在语音的数字通信和数字存储等应用领域,需要对多路语音信号进行实时采集和压缩处理。如某语音记录设备,需要对8路语音信号进行实时采集和压缩处理,而且要求对采集到的语音数据的压缩率尽量高。一般地,当要求语音数据压缩后的码流在10 Kbps左右时,需要采用语音的模型编码技术。而模型编码算法的运算量很大。因此,如一方面要求对多达8路的语音信号进行实时采集,另一方面又要求对各路的语音信号进行较高压缩率的实时压缩处理,对数据采集和处理系统提出了更高的要求。

由于VLSI技术的迅速发展,DSP(Digitalsig-nal processor数字信号处理器)的性能价格比得到了很大的提高,使得利用DSP的高速数据管理能力和处理能力来实现高速数据采集和处理成为实时数据采集和处理的一个新的发展方向。基于此,本文介绍的多路语音实时采集与压缩处理系统采用了高速DSP技术。

1 系统结构与工作原理

1.1 系统主要性能指标

采集语音信号通道数:8

语音信号带宽:300~3 400 Hz

采样速率:8 000 Hz

语音回放通道数:1

每路语音信号压缩后码流:13 Kbps

扩展ISA总线接口

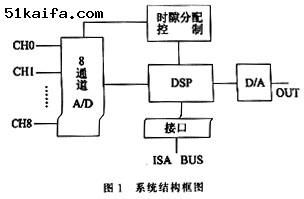

系统在结构上包括三个主要部分,即8通道A/D和1通道D/A部分,DSP最小系统及DSP的DMA与ISA总线的接口。如图1所示。

1.2 A/D及D/A

该部分由9片A-Law CODEC芯片TP3057组成。其中8片构成8通道A/D转换器,另一片构成D/A转换器,直接由DSP控制。该芯片采样数据是8 000×8 bit A-Law PCM数据,每通道数字信号的输入和输出是64 KbpsPCM同步串行码流。数据传输码流速率是2.048 Mb/s。8片A-Law CODEC均挂接在同一2.048 Mb/s的同步串行数据总线上,2.048 Mb/s的数据分为32个时隙,每个通道的64Kbps数据的传输占用32个时隙中的一个。具体占用那一个时隙由时隙分配控制电路确定。

1.3 DSP最小系统

DSP是本系统核心部分,它完成对2.048 Mb/s的同步串行数据总线的控制,及对高达2.048 Mb/s串行数据码流的采集、8路输入语音的压缩处理和1路语音的解压缩处理。本系统采用的DSP是AnalogDevice公司的定点DSP,即ADSP-2181,其主要功能与特点如下:

(1)外接16.67 MHz晶振,指令周期为30 ns,33 MIPS运算速度,所有指令单周期执行。

(2)提供一个16位的DMA(IDMA)口,用于高速存取片内存储器及装载数据和程序。

(3)提供一个8位自举DMA(BDMA)口,用于从自举程序存储器中装载数据和程序。

(4)程序RAM 24Bit×16 K,数据RAM 16Bit×16 K。

(5)16位字长运算精度。

(6)提供两个双缓冲区的串口,具有硬件A/u律编解码和自动缓冲(Auto-buffer)能力,其中的串口0具有多通道(Multichannel)的功能。

(7)提供6个外部中断、13个可编程I/O引脚和JTAG仿真引脚。

由于DSP的上述功能和特点,使得DSP与A/D及D/A电路实现了无缝连接。其中串口0连接8路A/D的2.048 Mb/s的同步串行数据总线,串口1连接D/A CODEC电路。由于DSP具有16 K的程序RAM和16 K的数据RAM,所以对于本系统无需外扩存储器,即由单片DSP就构成了本系统所需的最小DSP系统。

1.4 DSP的DMA与ISA总线的接口

ADSP2181片内集成了一个直接访问其内部存储器的16位DMA端口(IDMA PORT)。主机通过此接口可以直接访问ADSP2181片内的程序和数据存储器的任一单元。因而主机可以通过此端口对DSP加载程序、下载程序、读取片内执行的状态、实现与DSP的数据传输等操作。IDMA端口总线的16位数据和地址是复用的。由于DSP的程序存储器是24位的,而DMA的数据总线宽度是16位,故对程序存储器操作时,分为两次,先对高16位操作,然后接着对最低8位操作。通过IDMA端口的存、取操作分如下两步进行:

·IDMA地址锁定操作

通过IDMA的地址锁存信号(IAL),将14比特的地址信息和1比特的存储器类型信息通过IDMA总线,在地址锁存信号(IAL)的降沿时被锁入到DSP片内的IDMA地址锁存器。14比特地址信息确定了ADSP片内的存储器地址,而存储器类型位用来区分操作是对程序存储器或数据存储器。

·数据存、取操作

当地址信息被放入到IDMAA寄存器中后,通过加IDMA的IWR,IRD信号,实现对片内的指定地址的信息进行读、写操作。每次读、写操作后存储器的地址值将自动的递增,为下一次的读写操作做好准备。

本系统中通过ISA总线的I/O操作及IDMA口对DSP的内部存储器进行访问的。通过硬件译码满足IDMA时序要求的控制信号IAL,IWR,IRD等及DSP的复位信号(RESET)。该接口占用了16个I/O地址空间。

1.5 通过IDMA端口装载程序

ADSP2181通过两种机制在上电、复位后自动装载DSP程序。两种机制由MMAP和BMODE两个引脚的电平控制。当MMAP=0,BMODE=1时,ADSP2181自动在系统复位时,通过IDMA端口由主机加载DSP程序。主机首先必须装载除程序的第一条指令外其它程序和数据到DSP的片内程序存储器,最后才写入对应程序RAM第一个单元的第一条指令。一当程序存储器的0地址被写入程序代码后,DSP立即从地址0开始执行程序。

- 基于TMS320C6701DSP线性调频信号数字脉冲压缩(05-14)

- 基于DSP的多路语音实时采集与压缩处理系统设计(07-09)

- 基于TMS320VC5509A的语音识别与控制系统(06-17)

- 基于DSP的声控电子记事本的设计与实现(09-22)

- 基于DSP的安全无线多媒体数字终端(03-03)

- 基于DSP的通用型嵌入式语音平台的硬件设计(03-27)