利用以太网硬件在环路实现高带宽DSP仿真方案

通常情况下,在设计基于FPGA的大型信号处理系统的时候,设计人员往往需要进行费时费力的仿真。以Xilinx System Generator for DSP为代表的FPGA设计工具,通过提供可靠的硬件在环接口(该接口可以直接将FPGA硬件置入设计仿真),来解决这种问题。

通过在硬件上模拟部分设计,这些接口可以大大提高仿真的速度--通常可以提高一个甚至多个数量级。使用硬件在环还可以让设计人员实时进行FPGA硬件调试和验证。

System Generator for DSP 可以为多类FPGA开发平台提供硬件在环接口。这些平台通常通过不同的物理接口和PC建立通信。举例来说,一个JTAG协仿真接口可以允许任何一个具备JTAG头和Xilinx FPGA的FPGA板在System Generator for DSP内部进行协仿真。其它类型的板卡,比如XtremeDSPTM开发工具套件,是通过PCI总线进行通信的。直到最近以来,具有高存储带宽和吞吐率要求的系统协仿真(例如视频和图像处理),还只能在那些通过PCI或者是PCMCIA接口直接与PC建立通信的开发板上进行。

基于以太网的协仿真

System Generator for DSP 8.1内含一个全新的以太网协仿真接口,该接口首次让Xilinx ML402 评估平台具备了高带宽协仿真的能力。ML402开发板将直接通过标准以太网电缆或者通过网络远程连接到计算机上。

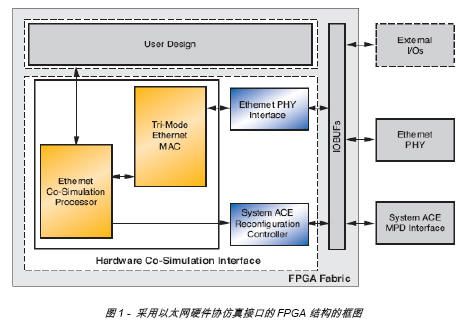

接口的核心是Xilinx三态以太网MAC核,它可以支持10/100/1000 Mbps半双工和全双工操作模式。当设计人员通过使用以太网硬件协仿真接口生成一个设计的时候,System Generator for DSP将自动在设计周围建立必要的逻辑,从而在仿真的过程中,通过以太网连接与FPGA进行通信(图1)。 你还可以双击任意一个设计的System Generator模块打开它的参数配置对话框,从而生成一个用于以太网硬件协仿真的设计。在编译菜单下,从硬件协仿真菜单中选择ML402/Ethernet编译(参见图2)。你可以在两种不同的以太网协仿真模式中进行选择。

基于网络的协仿真

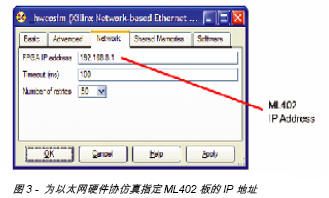

基于网络的接口可以让开发人员对那些连至标准IPv4网络的FPGA硬件进行协仿真。由于IPv4这种网络几乎无处不在,基于网络的接口,为与连接至有线或者无线网络的远程FPGA开发板建立通信提供了一条便捷的途径。该接口在后台管理着通信细节和错误处理过程(在丢包后重新进行传送)。System Generator for DSP通过分析ML402板的IP地址来决定在协仿真过程中与哪个平台进行通信(图3)。

点对点协仿真

第二种以太网协仿真的模式则是一种点对点接口,该接口使用原始的以太网帧,通过数据链路层与ML402板建立高带宽通信。与基于网络的模式不同的是,点对点接口侧重于本地网段上的低层通信。协仿真的数据则通过连接ML402板和计算机的标准UTP以太网电缆进行传送。这意味着,你的计算机必须具备一个空闲的以太网插口以建立连接。

点对点接口可以支持千兆位级以太网标准,如果该接口被配置为可以使用巨型帧,数据的传送性能将大大提高。使用这种接口连接方式,你甚至可以对超带宽应用进行协仿真。

器件配置

上述两种以太网协仿真接口都支持一种新的器件配置方法,即利用Xilinx System ACETM解决方案支持给予以太网的配置。这种配置过程可以在相同的用于协仿真的以太网连接上进行,因此消除了对二次编程电缆(如Xilinx Parallel Cable IV或者Platform Cable USB)的需求。ML402开发板还搭载了一个Compact Flash卡,它包含一个特殊的启动加载程序映像,该映像在上电的时候会自动下载至FPGA。该映像可以利用在仿真开始时通过以太网电缆传输的新的FPGA协仿真的数据位流对FPGA进行重新配置。整个配置过程都由System Generator for DSP以透明方式进行操控。

设计示例

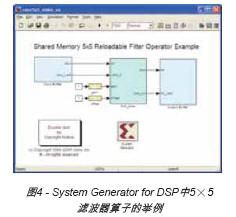

一个命名为conv5x5_video_ex的5×5滤波器算子设计模型被包含在System Generator for DSP 8.1软件工具当中。该设计证明了使用n-抽头MAC FIR滤波器可以有效地实现二维图像滤波。图4显示了System Generator for DSP的顶层设计。

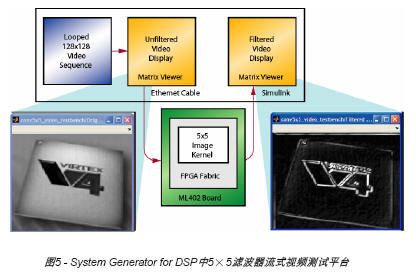

另外,该设计还包含一个硬件协仿真测试平台,该平台用来使循环视频序列以实时帧速率流过5×5内核。在每个仿真周期,视频帧将被传送到FPGA中进行处理。一旦进入FPGA,每个帧都会被5×5内核进行滤波,然后传回计算机用Simulink进行分析。仿真过程中,两个Simulink矩阵指示器模块分别显示未经滤波和经过滤波后的图像,图5所示为通过测试平台的数据流。

基准测试

对5×5滤波器设计示例进行了编译以便实现点对点以太网硬件协仿真,并利用Xilinx ML402开发板对其进行了协仿真。我们对硬件仿真速度与软件仿真速度进行了比较。基准程序特别考虑了每秒被读回的已处理帧的数目,并将结果同单个帧的滤波操作所耗费的软件仿真时间进行了比较。

- 基于以太网硬件在环路实现高带宽DSP仿真(07-07)

- 基于VHDL的AVS环路滤波器设计(06-05)

- 数字基带预失真系统中环路延迟估计的FPGA实现(06-05)

- 工业现场环路供电仪器仪表的四大关键设计环节(09-02)

- 有HART接口的完整4mA至20mA环路供电现场仪器(06-05)