基于CPLD的DSP多SPI端口通信设计

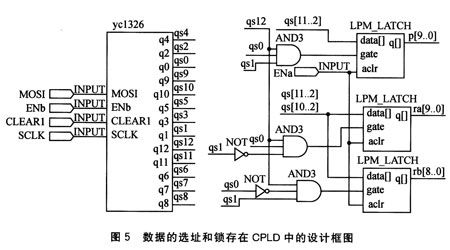

锁存器的工作特点:当gate引脚上输入高电平信号时,锁存器工作开始锁存总线上的数据;当gate引脚上是低电平时,锁存器不工作,即当总线上的数据发生变化时,锁存器的输出不发生变化。由于本设计需要多个参数传输,通过地址选择的方法把这3个数据从一条总线上区分出来,设置传输数据的低两位为地址选择位。地址选择位经移位寄存器,串并转换,作为三输入与门的两个输人端,进行地址选择。每次16位的数据移位结束,数据稳定时,在计数器高电平作用下,相应gate的引脚上输出高电平,数据锁存入相应的锁存器。例如,可以设置低两位是"ll"时,DSP送入PWM电路的是ll位的调相信号;当低两位设置成"01"时,DSP送入PwM电路的是10位调节A 相占空比的信号;当低两位设置成"10"时,。DSP送入PWM电路的是10位调节B相占空比的信号。由此可以在电路中设计一个三输入的与门,当16位数据传输完毕,即在相应gate的引脚上输出高电平时,数据存入对应的锁存器,如图5所示。

2.3 DSP与LTC6903的接口配置

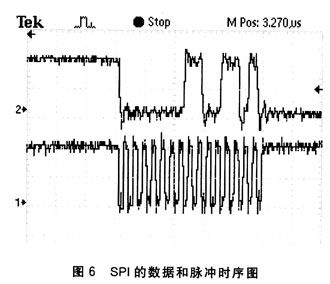

由于LTC6903芯片本身具有SPI接口,需要在DSP的程序中设置相应的SPI寄存器。LTC6903采用上升沿接收,且接收时高位在前,所以需要DSP设置为下降沿传输,传输时高位在前。在传输的过程中,在脉冲信号的下降沿数据发生变化,传输数据;在脉冲信号的上升沿数据稳定,便于LTC26903锁存数据,传输时序如图6 所示。从图中可以看出,所要传输的数据是十六进制数019A,下降沿数据发生变化,上升沿数据稳定,传输16位数据,有16个脉冲。实验结果表明,DSP 配置是与LTC26903的SPI接口工作时序相匹配的。

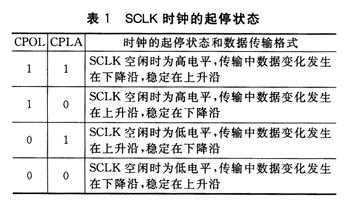

3 DSP中SPl的开发过程

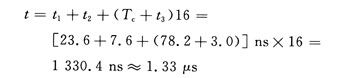

SPI端口数据传输的特点是:主设备的时钟信号出现与否决定数据传输的开始,一旦检测到时钟信号即开始传输,时钟信号无效后传输结束。这期间,从设备使能时钟信号的起停状态很重要[2]。 DSP56F801的SPI端口的时钟信号起停状态如表1所列。在设计中设置的SPI控制寄存器的CPOL和CPLA位是"11"。ScLK空闲时为高电平,传输中数据变化发生在下降沿,稳定在上升沿。从图2可看出实现了与CPLD中的移位锁存电路的匹配,传输正确。SPI端口协议要求系统上电复位后,从机先于主机开始工作。如果从机在主机之后开始工作,就有可能丢掉部分时钟信号,使得从机并不是从数据的第一位开始接收,造成数据流的不同步。可通过硬件延时或软件延时的方法,来确保从机先于主机工作口[2]。本设计采用软件延时的办法来实现数据流的同步。这个延时由两部分组成,一部分是DSP串行输出数据的时间延时,另外一部分就是后续数字电路中的延时。延时的具体计算过程如下:数据传输时使用的时钟信号是对总线时钟的2分频,当DSP的主频是60 MHz时,总线时钟频率是30MHz,对它进行2分频,可以计算出SCLK的周期是66.6ns(实际所测出的周期是78.2 ns)。另外通过测试得到PwM电路的延时最长时间是23.6 ns,锁存器的最大延时是7.6 ns,移位寄存器的最大延时是3.0 ns。由上述对CPLD数字电路的延时和对SCLK周期的测试,就可以得到这样一个结论:设PwM电路的延时时间为t1、锁存器的延时时间为t2、移位寄存器的延时时间为t3,SCLK的时钟周期是Tc,在SPI传输的过程中,整个电路的延时t可以这样计算:

由于数字电路传输中存在这样的延时,所以在写DSP程序时,需要加入一定的延时。此实验中加入的延时是2μs,可以实现可靠传输。

4 实验结果

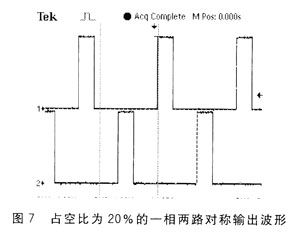

本设计采用全数字结构,易于用CPLD实现。以 EPM7256为目标芯片,设计并实现了正确的数据传输。当DSP56F801输出的十六进制参数分别为频率字DBOE,相位字0403,A相的占空比字 04CE,B相的占空比字04CD时,波形输出如图7、图8所示。图7给出了信号发生器A相输出信号的实测波形,信号占空比调节为20%;图8给出了A相输出信号1和B相输出信号1的实测波形,两相信号相位差调节为常用的90。。该实验结果表明,参数传输正确,波形输出良好。

结语

SPI通信方法具有硬件连接简单、使用方便等优点,应用广泛。采取硬件和软件相结合的措施,可以确保SPI通信中数据的同步,实现可靠通信。本文给出了DSP多SPI端口通信的实际与实现过程,讨论了其中的关键技术问题。SPI多端口通信方法基于CPLD实现,易移植,易于实现功能扩展,可广泛应用于各种采用SPI通信方式的自动化装置。

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)

- TMS320F240型DSP的SPI口的扩展 (02-20)

- 基于dsPIC30F2010的土壤水分测量仪的设计研究(08-27)

- 基于AD7862和dsPIC30F的数据采集系统(08-25)

- 基于DSPIC30F4011单片机的CAN总线通信设计(02-08)

- 采用SPI接口实现双DSP双向通信和同步(03-14)