SERDES的数字系统中高效时钟设计方案

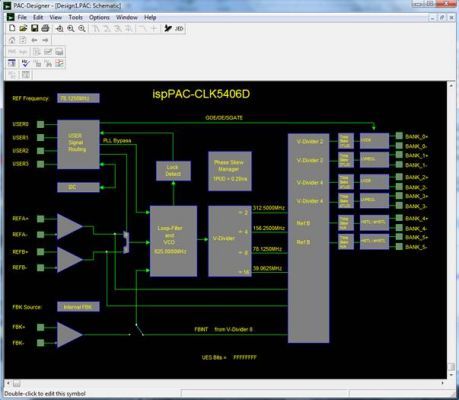

配置。配置ispClock5406D的GUI如图2所示。可通过该器件的框图定义不同的配置选项。用户只需简单地双击框图中的功能,然后会打开一个对话框,显示该功能的各种可编程选择。例如,在右上角的对话框中,用户可以输入参考时钟频率和反馈信号源。

图2:PAC-Designer5.2中显示的莱迪思ispClock5406D框图。

如图2所示,环路滤波器和VCO块的参考时钟输入源可以从REFA或REFB差分输入中选择。V分频器块使用环路滤波器和VCO块的输出来产生由PLL的几分频(2、4、8和16分频)决定的四种频率。来自输出V分频器块或用于外部反馈的FBK输入的反馈信号,提供了可与VCO"匹配"的参考时钟。如果选择输出V分频器块较小的分频数的信号来匹配输入参考时钟,其反馈信号将是选择较大分频数信号的几倍,这就产生了有效的频率是输入参考时钟源几倍的参考时钟源。在本示例中,将78.125MHz的输入参考时钟源加到REFA并将V分频器块的8分频输出作为反馈,则其8分频的输出为78.125MHz,4分频的输出为156.25MHz,2分频的输出为312.5MHz。

V分频器的输出频率可用于布线矩阵阵列,也可以分配给任意的isp5406D输出。每个输出都可以进行独立的相位和时间偏移设置,可以针对走线延迟来调整输出或其它细节方面的时序考虑。最后,输出类型可以从M-LVDS、LVDS、LVPECL、HCSLx6、HSTL/eHSTL、SSTL1.5V/SSTL1.8V或SSTL2.5V中任意选择。在示例设计中312.5MHz和156.25MHz信号可通过BANK_0至BANK_3的输出获得,使用LVDS和LVPECL标准。还可以选择REFB作为Bank4和Bank5的输出。这可以通过一些简单的时序调整来实现一个独立的时钟信号。

XAUI测试系统结果

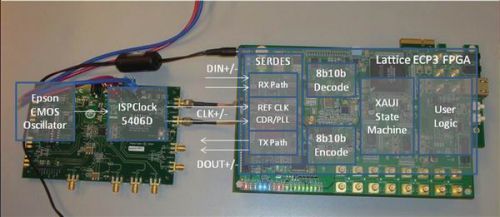

测试系统使用了ispClock5406D评估板和LatticeECP3FPGA开发板。测试建立的框图如图3所示,该设计中的开发板照片上标识了左侧是ispClock5406D板,右侧是ECP3FPGA板。(请注意,两个板之间使用SMA电缆传输时钟信号。这是一个比集成的时钟解决方案更具挑战性的信号环境。)

EpsonCMOS振荡器的工作频率为78.125MHz,用作ispClock5406D的参考时钟。ispClock5406D通过编程以4倍的参考频率即312.5MHz,用作使用LatticeECP3FPGA实现的XAUI设计的时钟源。使用片上ECP3的CDR/PLL块,实现了超低抖动、频率为312.5MHz10倍的参考时钟。3.125GHz时钟分配给高速的XAUI功能部分:SERDES的接收器(RX)和发送器(TX)块以及8b10b解码和编码块。

图3:使用ispClock5406D的XAUI系统。

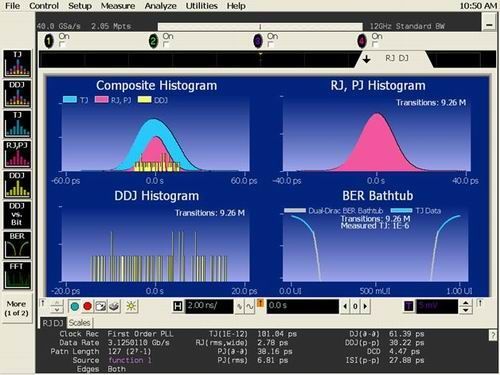

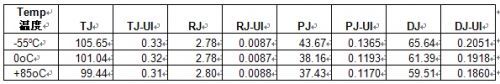

在抖动测试时,XAUI状态机通过编程输出标准的PRBS7测试图形。这从TX块和DOUT+/-信号上显示出来,标识于图3中LatticeECP3FPGA块的底部位置。这些输出连接到AgilentDSO-81304B的输入,以获取详细的抖动数据。图4以图形形式显示了0℃下的重要测量结果。在-55℃和+85℃下也进行了类似的测量。图4底部的表格显示了测试过程中的关键抖动测量结果。总抖动测量值需满足120ps(0.35UI)的XAUI标准,即时在最差的情况下,当超过-55℃至+85℃温度时,也必须满足105.65ps和0.33UI。同样,这些符合标准的结果是在使用两块独立的开发板的情况下取得的。使用一块板的话应该产生更低的抖动结果。

图4:抖动测试结果。

表1

ispClock5406D的配置存储在片上非易失性存储器中,可通过JTAG接口进行再编程。器件上的许多功能还可以通过I2C接口进行"即时"修改。基于ispClock5406D的系统的可编程特性支持许多附加功能,包括:TH和TCO时序裕度测量,有助于设计稳定性的测试;使用发送和接收通道间独立的偏移时钟的裕度测试,提高了可制造性;在数据有效窗口的中心进行准确的时钟对齐,增强了系统的可靠性。

- 展望未来 多核DSP技术不仅仅是小把戏(04-03)

- 基于SERDES的数字系统中高效时钟设计方案(06-05)

- 视频SERDES接口IC可优化远程及遥测应用(01-03)

- 低压差分SerDes的全双工互连和分组数据传输技术(12-25)

- 基于CPLD/FPGA的出租车计费系统(06-06)