基于DSP平台的USB接口设计

作者:汤金宽 吴裕冰 曹丹华

USB接口(Universal Serial Bus)是一种通用的高速串行接口。它最主要的特点是它的高速传输特性。USB1.1理论速度极限可以达到12Mb/s,USB2.0可达到 480Mb/s。这样,它可以很好解决大数据量的数据在嵌入式系统与PC机之间的互传问题;同时,它支持热插拔,并且最多同时支持127个外设,非常适合嵌入式系统的应用。

本次设计是在一个已有的DSP图像采集嵌入式系统的基础上,为它配接上一个USB1.1的接口,以达到DSP图像采集系统高速地将图像数据回传到PC机中的目的。设计的要求主要有:

①在原有平台提供的接口基础上,加入一个低成本、高速度的USB接口;

②通过USB接口,实现PC机对DSP图像采集系统的操作与控制;

③实现图像数据在DSP摄像系统与PC机之间高速的双向传输。

基于以上几点可以看出,本方案最主要的特点是成本低廉且传输速度高。

1 硬件方案选择与设计

1.1 方案选择

对于基于DSP平台的USB接口设计,经过综合考虑了几种方案之后决定,采用一个不带MCU内核的USB接口芯片PDIUSBD12(成 本非常低,一片PDIUSBD12的价格仅为20元),再加上简单的外围电路和时序调整电路。

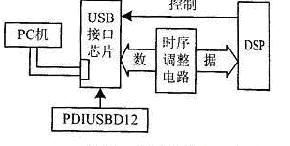

这种芯片仅仅完成USB底层的数据链路级交换,并提供给本地微控制器一个并行的接口,但是它并不完成协议层的工作。协议层的工作需要对微控制器 编程,控制USB接口芯片来实现USB协议。所以,开发难度相对来说大一些,要做的编程工作也多一点。但是这套方案的成本非常低,而且由于直接用DSP作 为微控制器,没有原单片机的瓶颈限制,所以可以实现很高的数据传输速率。该系统的原理框图如图1所示。

图1 该系统的原理框图

由于PDIUSBD12的并行接口时序较慢,只能达到2MB/s。这个速度相对于DSP来说比较低,而且有些地方不是简单地在程序中加入延时就 可以调整,所以需要一个时序调整电路来完成它们之间的配合。

1.2 PDIUSBD12芯片

PDIUSBD12芯片是由Philips公司推出的一种USB1.1接口芯片。它可以工作在5V或者3.3V的工作电压下;具有8位数据总线,且有完全自治的DMA传输操作。它还具有可控制的软件连接(SoftConnect)功能,可以保证在微控制器可靠完成初始化之后再连接上USB总 线。另外,它还有一个LED驱动脚,可以外接LED来监测USB的枚举过程和数据传输过程。当USB接口枚举完成,并且成功配置以后,LED将会一直点亮;而在枚举过程以及USB数据通信过程中,LED只是有节奏地闪烁。

PDIUSBD12只占用微控制器的两个地址资源。也就是说,它只有一根地址线。其中一个地址用来向芯片中写命令,另外一个地址用来向燕片中写 数据或者从芯片中读取数据。

PDIUSBD12一共有三组端点:端点0完成控制传输;端点1可以配置成中断传输;端点2是主要的数据传输端点。它有64B的缓冲区,如果加上它的双缓冲机制,就有128B的缓冲区;它可以配置成批量传输模式,或者同步传输模式。

总的来说,PDIUSBD12是一款性能优异,价格相对软低的USB接口芯片。

1.3 时序芯片

为了降低成本、简化电路,本方案不使用DMA传输方式,而以TI公司的TMS320C2XX作为微控 制器(使用20MHz晶振)。它的并口速度非常高,远远高于PDIUSBD12所要求的最高限制2MB/s。此处是硬件设计最关键的地方。

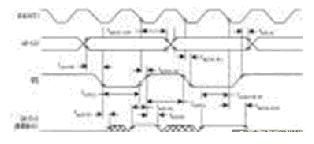

经过详细的时序分析发现,大部分问题可以通过在DSP固件设计的加入延时,或者设置DSP的WSGR寄存器来解决。但是有一个问题,必须在硬件 上加以解决。图2是DSP(TMS320C2XX)的写时序。

图2 DSP(TMS320C2XX)的写时序

图2中,参数th(W-D)是指在WE信号变高(无效)以后,所写的数据将仍然保持有效的时间。这个值最小为3ns,最大为14ns,所以所写的数据在 WE信号无效以后还会维持有效,大约3~14ns(实际的延时介于这两个值之间)。

图3是PDIUSBD12所要求的写时序。图中,参量tWDH是与DSP (TMS320C2XX)参量th(W-D)相对应的另外一个参量。这个参量反映了PDIUSBD12要求微控制器在向其中写数据时,所写的数据在WR信号无效之后,要继续保持有效的时间。这个参量最小值为10ns。也就是说,PDIUSBD12要求所写的数据最少要保持有效10ns(在WR无效之后)。

图3 PDIUSBD12所要求的写时序

由此可以看出,DSP(TMS320C2XX)的写时序不能可靠地保证满足 PDIUSBD12的要求,而且这个问题无法通过软件加延时的方法来解决,必须通过硬件来处理。经过分析对比,最后决定采用一个很简单但是后来事实证明非 常有效的方法来调整它们之间的时序。那就是在DSP(TMS320C2XX)与PDIUSBD12的总线之间加一个双向缓冲器-74LS245。这个芯片 可以在它们的时序之间引入一个延时。虽然这个延时并不可靠、但是由于DSP(TMS320C2XX)本身会在WR无效后,继续保持数据有效一段时间(前面 已讲过),这要仅仅需要将延时适当延长一点就可以了。74LS245所造成的延时典型值为15ns,最小也为8ns。这样,加上原来DSP写时序的延时, 就可以满足PDIUSBD12所要求的写时序了。

USB PDIUSBD12 DSP TMS320C2XX 相关文章:

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)