基于PCI总线数字信号处理机的硬件设计

时间:07-16

来源:

点击:

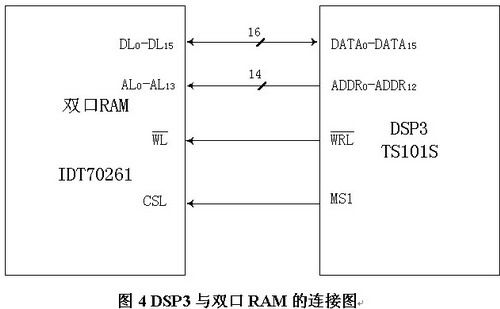

双口RAM作DSP3(TS 101S)输出暂存,故与DSP3的WRL相连。DSP3与双口RAM的连接如图4:

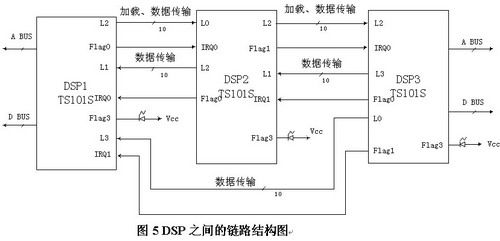

本系统采用DSP片之间以链路口互连方式,每对DSP间保留2个链路通道,总数据速率可达500Mbyte/S。采用链路口互连可以大大简化PCB板的复杂度。链路口互连是ADSP系列芯片的特有功能,也是ADSP处理器能以低成本组成多片高性能信号处理机的主要因素。DSP间的连接如图5:

结束语

本系统用于从外部采集信号,经数字信号处理机上的DSP芯片做信号处理,然后实现与PC机实时传输及数据存储,因此可对信号处理结果进行实时更新,从而实现数字信号处理机与相应设备间的高速数据传输。本系统还可应用于高速数据采集卡、视频处理卡、网卡等高速设备中。其中TigerSHARC系列芯片以其强大的运算能力从而大大的降低了开发成本,同时信号处理机的研制周期也可大为缩短,更容易的研制出性价比更高的信号处理机。而PCI 9054 以其强大的功能和简单的用户接口,为PCI总线接口的开发提供了一种简洁的方法,本系统经过测试,高速数据能够正确采集和传输。在高速数据传输系统中,利用PCI总线的高速特性实时传输和存储采集数据,有效解决了数据的传输和处理的实时性,随着PCI总线的普及应用,基于PCI总线的传输系统设计有十分广阔的前景。

- Linux系统对ISA总线DMA的实现(06-19)

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 对TTCAN的分析(05-26)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)