无线通讯标准千变万化 4G数据机迈向弹性化

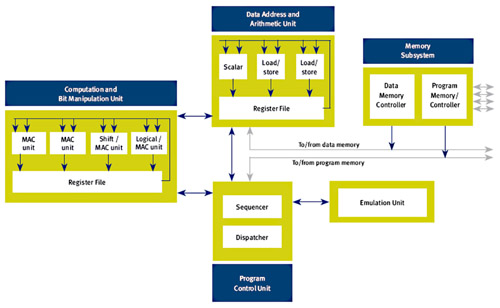

功能方块图。

|

图1 可支援VLIW和SIMD的混合式DSP核心功能方块图 |

以CEVA-X1641的DSP核心为例,这是一款具备四个乘累加器(MAC)单元的嵌入式DSP,由四个资料宽度为16位元的MAC单元组成。若芯片制造商以65奈米制程来实现此一核心,即便是在最差的条件下,该核心的运行时脉也能高达700MHz。

这种高性能且易于使用的DSP针对移动数据机系统单芯片(SoC)提供多个软硬体分区。不同的基频客户能在自己的数据机设计中,采用从单核心到多核心的不同实现方案和分区,并结合不同的硬体加速器来完成数据机功能。

SDR设计考验DSP核心

除了前文所提的混合式架构外,目前业界也开始出现软体定义无线电概念的实作芯片方案。如果要开发出在功耗、成本、尺寸等各个面向上均具备市场竞争力的软体定义无线电数据机,则必须更小心地评估其所采用的DSP核心。因为在此架构下,数据机的所有核心功能都是透过DSP和软体演算法来实现的。

若选择软体定义无线电架构,其芯片所采用的DSP核心通常必须针对先进的无线通讯而设计与最佳化,以确保其运算能力可以支援各种不同移动宽频标准。

目前在DSP核心授权市场上,已有足堪担此重任的DSP核心问世,可支援要求最严苛的4G移动标准如第五类LTE(LTE Cat. 5)和IEEE 802.16m,而且也能同时兼容现有的3G与3.5G无线通讯标准。也唯有采用能满足上述标准所立下的效能门槛的DSP核心,芯片供应商才能同时在单一架构中支援多种无线介面,实现真正的软体式数据机。

这类DSP核心是以单一引擎来完成所有无线处理工作,毋须仰赖多颗基频辅助处理器。对于软体定义无线电数据机的商品化而言,至关重要,因为以往的软体定义无线电方案通常是以一颗主DSP芯片搭配基频辅助处理器的方式实现。

这类分散式架构除采用多颗处理器外,还必须采用额外的记忆体、资料缓冲器等元件,因此整个系统的功耗和尺寸相当可观,成本亦过于高昂。

事实上,软体无线电架构以往只有军事或航太通讯产品采用,与系统尺寸过大、功耗太高、价格高昂这三项因素有密不可分的关系。若软体定义无线电技术要应用在移动数据机等消费性市场上,势必要设法妥善解决这三大难题。

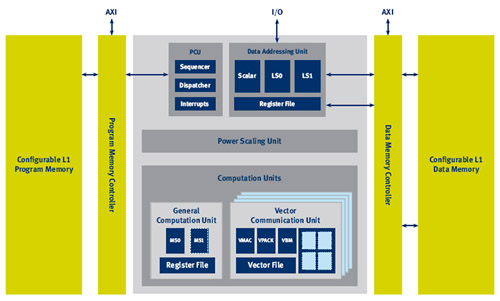

为了解决上述三大缺陷,专为软体定义无线电通讯应用所设计和最佳化的DSP核心中,除了部分DSP功能区块外,还整合了数量不等的向量通讯单元(Vector Communications Unit)。每个向量单元是一个256位元SIMD引擎,采用三路VLIW和大量16位元MAC、演算法、逻辑及位移单元。

透过这些向量通讯单元的帮助,这些特殊化的DSP核心可以满足4G无线数据机的要求,包括矩阵处理、多重输入多重输出(MIMO)检测器、复杂滤波、资料交换和位元流处理。图2为内建向量通讯单元的DSP核心功能方块图。

图2 专为SDR所设计的DSP核新功能方块图

弹性化设计势在必行

随着无线通讯产业朝向4G发展,因开发成本和多个变化标准的问题,使传统以硬体线路为基础的设计方案的风险大增。所以,设计一个能够迅速适应不断变化的标准,并可在多代产品上重复使用的灵活解决方案至关重要。

以混合式方案或全软体式数据机为基础的可编程设计解决方案,正式因应此一趋势而诞生的产物。可编程方案能让设计团队轻松地套用先前所完成的设计,并确保产品能快速上市。

无线基频领导厂商早已认可转向可程式设计解决方案的发展趋势,而投入DSP架构标准化的工作。在DSP核心标准化后,芯片厂商可以更轻松地根据其系统架构和灵活性水准选择正确的DSP核心。而且,最新的节能和制程几何尺寸缩小技术,也使得这些可编程设计方案渐渐成为多种应用中实现4G方案的首选方法。

(本文作者为CEVA产品市场总监)