基于USB和DSP的数据采集系统的设计

摘 要:介绍了一种利用USB2.0的高速传输特性,基于USB和DSP的数据采集系统。详细论述了系统的总体结构、部分硬件设计,并简要叙述了相应固件程序的实现。

关键词:USB DSP FPGA 高速传输

测量仪器一般由数据采集、数据分析和显示三部分组成,而数据分析和显示可以由PC机的软件来完成,因此只要额外提供一定的数据采集硬件就可以和PC机组成测量仪器。这种基于PC机的测量仪器被称为虚拟仪器[1]。而在一些数据量比较大、采集时间比较长的场合,就需要采用高速的数据传输通道。基于虚拟仪器的思想和高速传输通道的要求,设计了一种基于DSP和USB2.0的高速数据传输接口。

1 数据采集系统硬件

数据采集系统由A/D数据采集单元、USB从接口单元、U盘读写单元组成。硬件原理图如图1所示。被测信号经A/D转换后写入FIFO中;当FIFO数据半满后,产生中断,通知DSP进行数据压缩处理;DSP把压缩好的数据依次写入USB接口芯片的4个从FIFO中,4个从FIFO对应USB的4个端点,DSP一边写入数据,已写满的从FIFO就一边通过相应端点由SIE把数据发送到上位机,上位机一边把收到的数据通过多线程存储到硬盘中,一边把数据解压并把波形实时显示出来。对于少量的数据,可以存储到U盘,送回PC机进行分析显示。

1.1 A/D采集模块

作为单通道输入的MAX1189,主要控制信号有CS、R/C(Read/Conversion)、EOC(End of Conversion)。图2为MAX1189的时序图[2]。如图2所示,每个采样周期长达CS信号的三个周期。在第一个CS信号的下降沿,如果R/C为低电平,也就进入了应答模式,这是开始采样前必须的准备工作。为了适应不同的输入极性要求,MAX1189的内部参考电压可以在每次转换结束后进行设置,这是通过在第二个CS下降沿时,R/C的高低电平变化来控制的,非常简便。低电平时,ADC内部参考电压无需进行转换,这样在开始下一个周期的转换时无需等待电压的变化。高电平时,内部参考电压会进行调变,这样在开始下一周期的转换时需要等待大约12?滋s的时间。在CS信号的第三个下降沿,EOC信号变为低电平,表示采样结束,此时R/C信号为高电平,会把采样数据放到总线上,这样就完成了一个周期的采样。采样模块的控制信号是由FPGA控制的。

1.2 DSP与FIFO的连接

主处理器DSP既要控制采集,又要完成数据的处理和传输,因此数据采集模块采集来的数据不能直接传送给DSP,这会极大影响DSP的处理效率。解决办法是利用数据缓冲器如双口RAM、FIFO等,对数据进行适度缓存,当缓存的数据量达到一个设定值时,可以通知CPU进行一次高速数据传输,将缓存的数据一次性地读入。在设计中采用了缓冲,较好地解决了采集端与处理端的速度匹配问题。

FIFO的读写由各自的控制时钟FIFOR和FIFOW控制,写时钟与采样时钟同步,读时钟与DSP处理数据的时序有关。当FIFO半满后,FPGA会根据FIFOHF、FIFOE/F、FIFOPAFE的相应位判断FIFO是否半满,FPGA便向DSP发出中断请求。本设计中采用外部中断的EXTINT3来作为FIFO缓冲数据的DMA传输触发事件。DSP响应FPGA中断请求,读取数据进行数据压缩。当DSP数据处理速度跟不上采集数据速度时,FIFO就会全满,FPGA根据FIFOHF、FIFOE/F、FIFOPAFE相应位状态判断到FIFO已全满,于是向USB接口芯片单片机发出最高级中断请求,通知系统数据己溢出,采集发生严重错误。

1.3 USB从接口电路

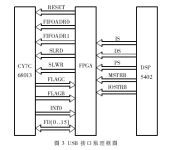

USB从接口单元采用CYPRESS的CY7C68013芯片。如图3所示,USB接口芯片CY7C68013由3.3V电源供电。PAO/INTO#选择INTO工作方式,其中断级别最高,当FIFO全满造成数据溢出导致数据采集发生严重错误时,该中断请求发生,系统通知数据溢出错误,并停止数据采集。RESET#为USB接口芯片复位输入。

USB的FDO~FDl5与DSP的I/O数据线相连,用于DSP与USB从FIFO通信,SLWR为写控制时钟。FLAGB、FLAGC用于输出2,4,6,8相应端点从FIFO的空满状态,以便DSP写USB从FIFO时获取空满状态。

FIFOADRO、FIFOADR1用于DSP寻址2,4,6,8相应端点USB从FIFO,FIFOADRO及FIFOADR1功能真值表如表1所示。FIFOADRO、FIFOADR1的初值为00,对应DSP写端点2的从FIFO, FPGA对写USB从FIFO的控制时钟SLWR计数,当达到512次时,表示端点2己写满,计数器清零,FIFOADRO和FIFOADR1的值自加一次变为01,对应DSP写端点4的从FIFO。以此类推,DSP依次写2,4,6,8端点数据,当FIFOADRO和FIFOADR1的值为11时,再自加一次,FIFOADRO和FIFOADR1的值又变为00,因此,DSP可循环写2,4,6,8端点。需要说明的是,当DSP开始写一新端点的从FIFO之前,DSP要读一次FLAGB、FLAGC标志位,若该端点不空,则等待;若空,则进行写数据操作[3]。

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)