基于ARM智能交通信号机控制板开发

1 引言

目前我国的城市交通控制主要还是靠道路交通信号控制机(以下简称信号机)。国内的信号机主要分为两类:一类采用8/16位单片机作为处理器,交通控制功能简单、方案单一,以RS 232或RS485为通讯方式,难以与控制中心联网以及实现区域交通协调控制等功能,不能适应现代化大路口交通控制的要求;另一类则是基于工控机或PC104,功能虽然强大,但由于工控机或PC104都是按通用计算机标准设计,并非专门针对信号机应用设计,该类信号机硬件结构复杂且很多功能并不需要,成本也高,国外的信号机(如西门子公司的2070和美国的EAGLE)开发起步早,水平高,已有各种自适应联网型信号机产品,但一般不适用于中国混合交通的实际情况,且价格昂贵,操作不方便。

信号机是一个典刑的嵌入式系统,嵌入式系统是以应用为中心来设计,对功能、性能、可靠性、成本、功耗、体积等有严格的要求,既要满足智能交通系统对信号机智能化、多功能的要求,又要最大化信号机的性价比,因此本设计选择基于ARM核的32位嵌入式RISC处理器--AT91RM9200来完成智能交通信号机控制板的硬件设计,以达到使信号机在交通系统中成为收集与处理交通流量数据、通信联网以及区域协调控制平台的设计目标。

2 信号机系统硬件设计

2.1 系统总体硬件结构

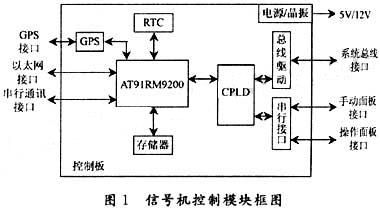

智能交通系统要求信号机可以向控制中心实时提供多种道路信息和车流量数据信息,接收控制中心的控制命令,并能够独立执行一些复杂的算法,可以根据交通流量变化实时条件路口信号灯的绿灯时间,因此考虑现有信号机的不足,根据信号机功能发展的趋势和要求,本文设计的信号机控制板具有控制参数输入、控制状态输出、控制参数保存、灯态输出控制、交通流信息(主要是车流量)实时检测与历史数据存储、多种灯态控制方案与算法模型存储、支持以太网及与手持终端设备通讯等基本功能。整个系统硬件结构如图1所示。

2.1.1 AT91RM9200微处理器介绍

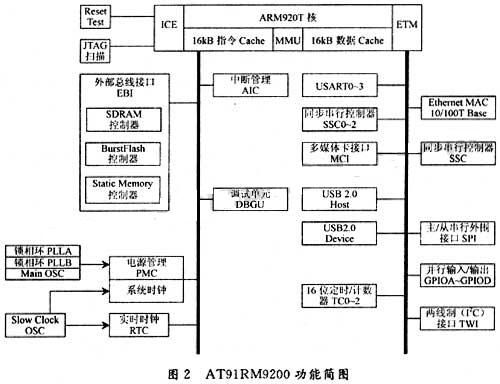

嵌入式微处理器是整个嵌入式系统的核心,AT91RM9200是Atmel公司推出的基于当前流行的ARM920T内核的一款32位RISC微控制器,工作在180MHz频率下的运算速度可达200MIPS。专门针对系统控制、通讯领域的应用。AT91RM9200芯片的功能结构如图2所示。

AT91RM9200集成了丰富的外围功能模块,满足多种应用场合,丰富适合于实时控制,可以支持实时操作系统(RTOS),为需要多功能、低成本、低功耗的计算密集型应用提供了一个单芯片级的解决方案。AT91RM9200是一款性价比极高的微处理器,经过比较选择AT91RM9200作为信号机控制板处理器。

2.1.2 控制板外围模块

控制板设计主要包括以下几个部分:

(1)电源/晶振模块:

控制主板使用12/5V两套电源供电,AT91RM9200工作于3.3/1.8V两种电压,系统其他器件尽量选择工作电压为3.3V。

AT91RM9200使用12MHz/32.768kHz两种晶振,主晶振12MHz经过芯片内倍频处理分别为ARM920T核与系统提供180MHz和60MHz的时钟频率。32.768kHz慢时钟用于AT91RM9200的启动。

(2)存储器模块。

(3)网络模块。

(4)串口模块和GPS接口:

AT91RM9200提供4个USART,分别将他们分配给RS232和RS485。控制板上预留GPS接口位置,用于未来扩展信号机无线通讯功能,GPS使用RS232同AT91RM9200通信。

(5)RTC模块:

信号机在通讯、干线或者区域协调控制中需要使用统一的时间来同步,因此设计RTC(实时时钟)用来对时。RTC可以提供可编程的实时时钟:年(含闰年)、月、日、时、分、秒、星期及一个闹钟中断,并可以在掉电后使用备用电源工作。

(6)系统总线扩展模块。

2.2 主要硬件模块电路设计

下面详细说明存储单元、网络和系统总线扩展模块的硬件设计。

2.2.1 存储器模块

本文设计的信号机需要存放嵌入式操作系统及其文件系统、应用程序和其他在运行或系统掉电后需要保存的数据;另外当系统启动后,操作系统和程序运行还需要更大的空间。AT91RM9200内部集成的ROM和RAM的容量不能够满足信号机的要求,因此设计了外存储单元来扩展存储空间,由16MB和FLASH和64MB的SDRAM组成信号机的外存储系统。

AT91RM9200的地址空间是4GB,他被划分成16个256MB的区域;

区域0为内部存储器空间;

区域1-8是给由EBI控制的外部设备(扩展的片外存储器和外接的设备)使用的,片选信号为引脚NCS0-7;

区域15是AT91RM9200集成的片内外围功能(包括系统和用户外围)使用的地址空间,当系统上电或重启时,根据引脚BMS的电平状态,系统选择是从内部ROM(BMS=1)还是从存储区域1即NCS0片选区域(BMS=0)启动。

(1)本设计选用1片8M×16b数据宽度的FLASH,共16MB,作为

- Linux嵌入式系统开发平台选型探讨(11-09)

- 嵌入式系统中文输入法的设计(03-02)

- 基于MPC755的嵌入式计算机系统设计(05-10)

- WinCE下光电编码器的驱动程序设计(04-12)

- 为什么嵌入式开发人员要使用FPGA(05-13)

- VxWorks几种常用的延时方法介绍(05-16)