DSP片外高速海量SDRAM存储系统设计

含1个页面寄存器(只对配置为SDRAM空间有效),因此C620X每个CE空间1次只能激活1页。进行比较的地址位数取决于SDCTL寄存器中SDWID位的值。如果SDWID=O,该CE空间构成页面的大小为512,比较的逻辑地址是位23~11;如果SDWID=1,该CE空间SDRAM构成页面的大小为256,比较的逻辑地址是位23~10。一旦发现存取访问发生了页面越界,EMIF会自动执行DCAB操作,然后再开始新的行访问。

2.4访问地址的移位

由于SDRAM行逻辑地址与列逻辑地址复用相同的EMIF 引脚,所以EMIF接口需要对行地址与列地址进行相应的移位处理。地址的移位处理由SDCRL寄存器中的SDWlD位控制。 另外,对于SDRAM,因为输入地址也是控制信号,因此需要说明以下几点:

①RAS有效期间的高位地址信号会被EMIF内部SDRAM控制器锁存,以保证执行READ和WRT命令时选通正确的bank;

②READ/WRT操作期间,EMIF会保持pre-charge信号为低(C620X是SDAl0),以防止READ/WRT命令执行后发生auto pre-charge操作。

2.5接口时序的设计

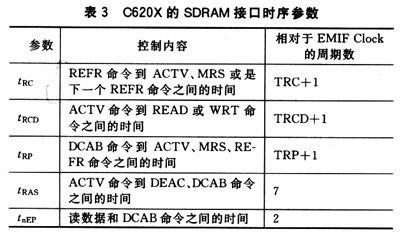

对于C620X,EMIF与SDRAM的接口时序由SDCTL寄存器控制。EMIF提供了5个时序参数,其中3个在SDCTL寄存器中设置,另外2个为固定值,如表3所列。在分析接口时序的配合情况时,需要计算"富裕时间"tmargin的大小,这是在考虑了SDRAM芯片的器件手册提供的最坏情况之后,得到的时序上的一个裕量。至于tmargin值的大小,是系统设计层需要考虑的问题,具体要求随不同的系统而异,而且与印制板的实际布线情况以及负载的情况密切相关。

3 系统设计中IS42S16400芯片的应用

3.1 C6201与IS42S16400的接口实现

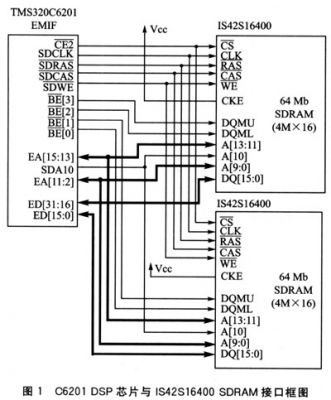

由于IS42S16400属于16位字宽的64 Mb SDRAM芯片,而C6201的EMIF只提供32位字宽的同步外存储接口,为了使整个系统的存储空间保持连续,使用2片SDRAM与DSP芯片组成实际大小为16 MB的外部存储系统,如图1所示。图1中IS42S16400芯片各引脚含义如下:CS,片选;CLK,系统同步时钟;RAS,行地址选择;CAS,列地址选择;WE,读/写使能;CKE,时钟使能;DQMU、DQML,高低字节使能;A[13:123],Bank地址选择线;A[11:0],行、列地址线;DQ[15:0],双向数据端口。

由图1可以看出,虽然C620l提供32位地址寻址能力,但是经EMIF直接输出的地址信号只有EA[21:2]。一般情况下,EA2信号对应逻辑地址A2,但这并不意味着DSP芯片访问外存时只能进行word(32位)的存取。实际内部32位地址的最低2~3位经译码后由BEx输出,是能够控制字节访问的。更高位逻辑地址经译码后输出CE[3:0]。

在实际的系统实现中,C6201的CLKOUT1时钟频率为200 MHz,故而SDRAM的实际工作频率为100 MHz(SDCLK=CLKOUT2=CLKOUT1 frequency/2),即tcyc=10 ns。SDRAM被配置在CE2空问(起始逻辑地址为0x02000000)。

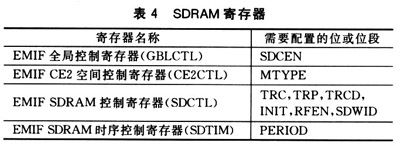

3.2 06201 EMIF SDRAM寄存器设置

表4列出了配置SDRAM需要设置的EMIF寄存器名称及相应的位或位段。

EMIF全局控制寄存器中的SDCEN位(位6)设置为1,用来使能SDRAM同步时钟SDCLK的输出。EMIFCE2空间控制寄存器中的MTYPE位段(位6~4)设置为011b,用来配置CE2为32位宽的SDRAM空间。由IS42S16400数据手册可查得tRC=70 ns、tRp=18 ns、tRCD=18 ns,故而EMIF SDRAM控制寄存器中的TRC位段(位15~12)应设置为0110b,TRP位段(位19~16)应设置为0001b,TRCD位段(位23~20)应设置为0001b。INIT位(位24)置1,用来强制对SDRAM进行上电初始化。RFEN位(位25)置1,用来使能EMIF对SDRAM的刷新。SDWID位(位26)置1,用来向EMIF表明所使用的SDRAM芯片的字宽为16位。由于IS42S16400的刷新频率为每64 ms 4096次,故根据公式PERIOD=trefesh/tcyc,EMIF SDRAM时序控制寄存器中的PERIOD位段(位11~O)被设置为0x61A。

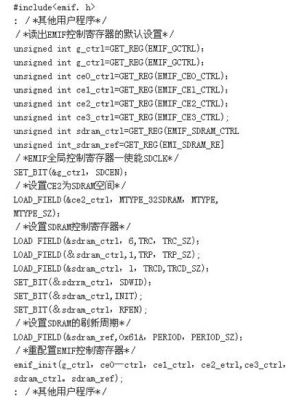

3.3 CCS开发环境中SDRAM配置程序源代码

TI公司的集成开发环境CCS(Code Composer Studio)中,IS42S16400SDRAM芯片的配置程序C代码如下:

结 语

以上介绍了TMS320C6201 DSP芯片与SDRAM(IS42S16400)的具体硬件接口实现。由于SDRAM具有的大容量、高速度和低价格的优势,使用SDRAM构建嵌入式应用海量存储系统会成为一种行之有效的方法。目前该系统已调试完毕。使用SDRAM作为DSP系统外接高速、大容量主存储器具有非常明显的优势,充分显示了SDRAM在嵌人式系统中的良好应用前景。

IS42S16400芯片 存储 SDRAM 相关文章:

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- 浅谈Win CE应用程序的可移植性(03-02)

- DSP与普通MCU的比较(02-23)