基于DSP的1553B总线系统设计与实现

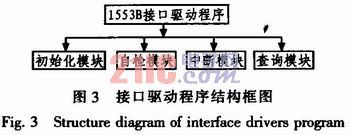

数据的接收和发送。整个驱动程序的组成如图3所示。

4.1 初始化模块设计

在驱动程序编制中,初始化模块是非常重要的一部分,作为整个程序的入口,初始化模块完成整个接口卡的初始配制,该模块主要功能为:

1)完成对F2812初始化,设置其相关寄存器,主要是设置有关中断和串口的寄存器,包括中断标志寄存器(IFR)、中断使能寄存器(IER)、中断控制寄存器(ICR)、SCI通信控制寄存器(SCICCR)、SCI控制寄存器l(SCICTL1)、波特率设置寄存器(SCIBAUD)等,以确定中断源和串口的波特率、停止位等。其具体操作为:①使IFR=Ox0000。IER=Ox0000,关闭所有的中断;②使IER=OxO101,开启中断SCITXRXINT和中断XINTl;③使ICR=0x001F,将中断模式设置为下降沿触发中断XINTl;④使SCICCR=0x0007;设置发送和接收中使用1 bit停止位,8 bit字符长度;⑤使SCICTL1=0x0003;使能发送器TX、接收器RX;⑥使SCIBAUD=Ox01E7,系统时钟SYSCLK的频率为150 MHz,低速外设时钟频率LSPCLOCK为37.5 MHz时,异步串行口数据传送波特率为9 600 b/s,BRR的数值可由公式得到。⑦SCICTL1=0x0023,使SCI退出复位。

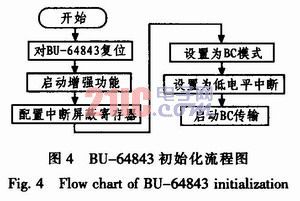

2)完成对BU-64843协议芯片内部寄存器(主要包括开始/复位寄存器、配置寄存器1、配置寄存器2、配置寄存器3、中断屏蔽寄存器)的初始化设置,使其能够正确实现BC模式的功能。BU-64843对片内功能寄存器的设置顺序有严格要求,如果顺序不正确将会引起芯片初始化失败。BU-64843工作在BC模式下的有关寄存器的配置顺序如下:①将开始,复位寄存器配置为0x0001,即可对BU-64843进行软件复位;②如果用到BU-64843增强模式,将配置寄存器3配置为Ox8000;③将中断屏蔽寄存器设置为Ox0001,使消息完成中断使能;④将配置寄存器1设置为BC模式;⑤将配置寄存器2设置为0x0008,使中断方式为低电平中断;⑥将开始/复位寄存器配置为Ox0002,启动BC传输模式。

通过对以上寄存器的配置。即可完成BC模式的操作。其初始化流程图如图4所示。

4.2 自检模块

自检模块主要完成对BU-64843的4 kB RAM空间的检查,看是否出现错误。实现方法是向该内存空间写入连续的数据,然后读出来比较看是否相等,若不相等则表示有错,记录下所有的错误数并把这个错误数通过串行口发送给上位机。

4.3 中断模块

驱动程序的中断模块分为2部分:1)用于接收1553B总线到来的数据,响应1553B总线数据的中断。利用F2812的XINTl,XINTl采用脉冲下降沿触发中断方式;2)用于接收上位机向DSP发送的命令,接收上位机的命令是通过F2812的串行通信接口(SCI)来进行的,利用F2812的SCIT-XRXINT中断。在XINTl中断服务子程序中设置"读总线数据标志",在异步串口中断服务子程序中设置"读串口数据命令标志"。在查询模块中,可以通过查询这两个标志,来判断是否有总线数据到来以及是否有上位机的命令到来。

4.4 查询模块

在查询模块中,当"读总线数据标志位"有效时,F2812就从BU-64843的命令堆栈相应地址处开始依次读4个地址单元的内容。分别为数据块状态字、时间标志字、数据块指针和接收到的命令字,根据命令字和数据块指针到数据堆栈读取总线数据,然后将接收到的总线上的数据转发出去。

当"读串口数据命令标志位"有效时,RX接收上位机的命令,根据不同的命令实现相应的功能。为了能够保证与上位机实现可靠的握手,在查询程序中设置了一个数据缓冲区,在查询程序中对缓冲区中的数据进行判断,看是否收到一帧完整的命令。若收到一帧完整的命令,则根据不同的命令设置系统的启动、停止、自检等相应标志,并将缓冲区中的数据依次向前移动一帧,数据指针也向前移动一帧。

5 结论

本文对1553B总线协议及其接口芯片BU-64843的功能、配置进行详细说明,并介绍了定点DSP TMS320F2812的基本性能和特点。在此基础上实现了基于F2812和BU-64843的1553B总线接口的硬件电路和软件的设计。BU-64843作为全3.3 V供电的1553B总线终端之一,方便与DSP芯片F2812连接。BU-64843芯片功能强大,同时设置也很复杂,因此,对接口芯片的掌握,不但要从硬件接口上入手,还要熟悉其内部寄存器的相关配置。基于DSP的1553B总线接口设计方案有效解决了通讯实时性要求高的问题,对地面电子检测系统的应用具有参考价值。

1553B 总线接口 DSP FPGA TMS320F2812 相关文章:

- 基于μC/OS-Ⅱ的1553B和ARINC429总线实时协议转换系统的设计(08-09)

- FPGA/DSP技术的1553B飞机总线系统通讯软件的设计(01-15)

- 基于LXI总线的1553B通讯模块设计与开发(11-24)

- 基于1553B总线的航天大功率电动舵机控制器设计(12-21)

- 基于FPGA的1553B总线接口设计(12-20)

- 1553B总线系统的可靠性研究(12-20)