基于 DSP 的视频算法系统优化若干策略

的缓冲帧,因此数据基本上无法在片内存放。为此在系统的Memory优化管理中,需要开C64系列DSP的二级Cache(对于TMS320DM642用于视频编解码中二级Cache开64k的情况比较多)。同时最好将放片外的被Cache所映射的视频缓冲区的数据以128 byte对齐,这是因为C64系列的DSP的二级Cache的每行大小为128 byte,以128 byte对齐有利于Cache的刷新和一致性维护。

算法系统集成时的EDMA的资源分配管理

由于在视频处理中,会经常有块数据的搬移,而且C64系列DSP提供了EDMA,逻辑上有64个通道,因此对EDMA的配置使用对优化系统是非常重要的。为此可以使用下述步骤进行充分配置系统的EDMA资源。

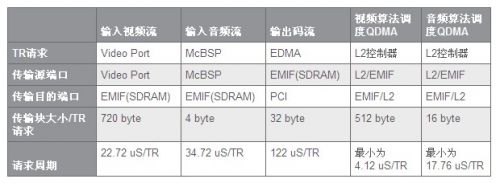

1. 统计系统中各种需要使用EDMA的情况及其大概需要占用的EDMA物理总线的时间,如表2所示:

注意:该表针对视频通过视频端口(Video Port)(720*480,4:2:0,30Frame/s),音频通过McBSP(采样率为44k)进入DSP,压缩好的数据数率在2Mbps左右,数据通过PCI每488uS输出一个128byte的包(PCI口工作频率为33MHz),外挂SDRAM的时钟频率为133MHz,只做一个参考应用例子。

2. 统计好这些信息后,需要依据系统对各种码流实时性、及其传输数据块大小对各个被使用的EDMA通道进行优先级分配。一般而言,由于音频流传输块小,因此占用EDMA总线的时间短,而视频传输块比较大,占用EDMA总线的时间较长,因此将输入音频所对应的EDMA通道的优先级设定为Q0(urgent),视频的优先级设定为Q2(medium),输出码流所对应的EDMA通道的优先级设定为Q1(high),音视频算法处理中所调度的QDMA的优先级设定为Q3(low)。当然这些设定在真正系统应用中可能还需要调整的。

实际的基于TI DSP视频算法优化集成过程,会是基于图1所示的步骤,先初步配置Memory,并选择相应编译优化选项,如果编译的结果已经可以达到实时性要求之后就结束后面的优化;否则开始优化Memory和EDMA的配置,从而提高对Cache和内部总线的利用率;如果还无法达到要求则通过剖析整个工程确定消耗CPU资源最高的代码段或者函数,对这些关键模块进行优化,采用线性汇编、甚至汇编直到整个系统可以满足要求为止。

参考文献:

TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (SPRU732)

TMS320C6000 EDMA IO Scheduling and Performance (SPRAA00)

TMS320C6000 Optimizing Compiler User's Guide (spru187)

TMS320C64x EDMA Architecture (SPRA994)

TMS320C6000 EDMA Controller Reference Guide (SPRU234)

TMS320C64x DSP Two-Level Internal Memory Reference Guide (SPRU610)

Cache Usage in High-Performance DSP Applications With the TMS320C64x (SPRA756)

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- 基于DSP的视频采集驱动程序的实现(07-21)

- 基于达芬奇技术的数字视频系统设计与实现(05-08)

- 基于DSP的数字视频采集系统的设计(02-19)

- 多路数字视频光纤传输系统的设计,软硬件架构(06-04)

- 什么是达芬奇(DaVinci)技术(12-07)