如何缩短嵌入式系统开发之路

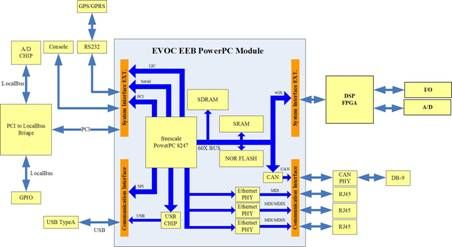

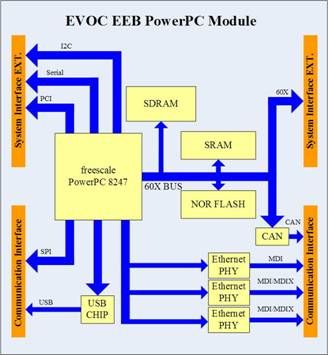

Irp一>相应的软件驱动。模拟电路的设计同样会遇到很多复杂的问题,限于篇幅本文不再赘述。 方案二:利用EVOC EEB PowerPC模块构建 采用这种方案,虽然通常来说需要付出比板卡组件成本更高的价钱,但是可以显著缩短产品进入市场的时间。除此之外,这些系统具有较好的可扩展性。随着处理器技术的进步,嵌入式系统出现以下几种不同的实现技术: 1、 非集成式嵌入式系统------对于使用现成产品来构建系统,这种系统通常是最为经济的解决方案。但是,针对这种系统的软件开发工具几乎从未集成,而且这些系统通常需要进行各种监管认证。 2、 集成式嵌入式系统------除了具有与非集成式嵌入式系统相同的组件,这种系统还提供诸如冲击、振动、工作温度,以及环境认证之类的技术说明。通常这些系统更加昂贵,但一般都带有集成的软件开发环境,且具有更为丰富的I/O选择。 3、 工业级PC------利用现成的PC技术,工业级PC为开发工具及I/O性能提供了更为丰富的选择。它们也具有许多与其他集成式嵌入式系统相同的技术说明和认证,但这种性能是以成本为代价的,它比前述两种方案更为昂贵。 基于EVOC EEB PowerPC模块的集成式嵌入式系统架构与图1所示的简单方框图相似。它使用Freescale PowerPC嵌入式处理器运行VxWorks或Linux实时操作系统。PowerPC通过内部的60X总线或PCI总线与DSP/FPGA相连接。 DSP/FPGA直接连接至AD采集芯片、开关量输入输出等外围接口。 图2:基于EVOC EEB PowerPC模块的集成式嵌入式系统示意图 图3:EVOC EEB PowerPC模块框架 纵观以上两种设计方案,技术性在其中能不能起到决定性作用,而简单的经济性分析却是非常必要的。如果最终的利润足大于开发过程中所花费的工程成本投资,那么所做的决定就是明智的。准确估算自行设计方案所花费的成本,并不是一个很简单的过程;如果只是把板卡组件的成本和硬件及软件的开发时间相加,那么只能是非常粗略地估算了总投资成本。还应该考虑其他的潜在成本才能准确地评估实际的任务成本。 评估了工程投资成本后,可使用公式: TPC/(SUP-VCUP)=BEP(其中,TFC为总固定成本,VCUP为单位变动成本, BEP为收支平衡点。)简单计算出企业的收支平衡点。但这并没有包含其他潜在成本。不过,如果选择了集成式嵌入式系统,不但可以缩短上市时间,而且早期的利润将会用于成本优化和特性改进。通过这种方案,可以在整个产品生命周期内分摊投资成本,而不是在早期的开发过程中投入所有资金。 那么这样是否就不用再自行设计板卡了呢?当然不是。对于那些对形状尺寸有具体要求且具有极高产量的系统,或者技术要求极为苛刻的系统来说,自行设计的方案将更具优势。而对于产量相对较低、技术复杂又需要快速上市的产品,使用现成平台可以让供应商负担物流和潜在成本,而使设计人员可以专注于突出技术优势,从而在市场竞争中处于领先位置。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)