基于DSP和SOPC数字信号发生器的设计

时间:01-05

来源:

点击:

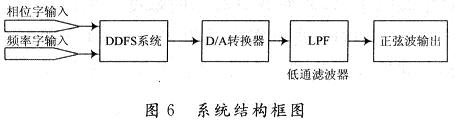

DDFS通过数控振荡器产生频率、相位可控的正弦波。其优点体现在无需相位反馈控制,频率建立及频率切换较快,可编程且全数字化,控制灵活方便,输出相位连续。如果在相位累加器的位数N足够大时,理论上可以获得很高的分辨精度,应用DDFS还可以产生其他多种调制信号,因此具有极高的性价比。

2.2 硬件模块设计与仿真

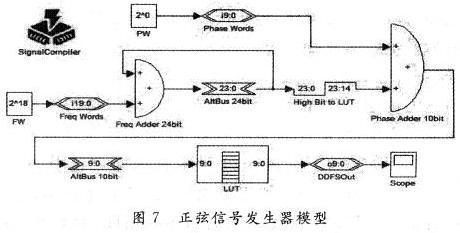

利用DSP BuiIder进行DSP模块设计是SOPC技术的一个组成部分。关键设计过程在Matlab的图形仿真环境Simulink中进行,用图形方式调用DSP Builder和其他Simulink库中,图形模块,构成系统级设计模块,如图7所示。

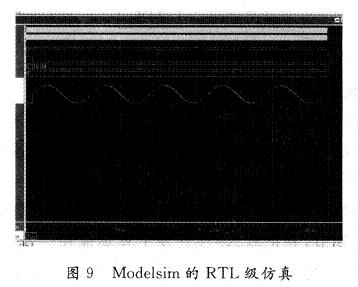

电路模型设计完成后,可以利用Simulink环境的强大的图形化仿真验证功能,直接进行算法级模型仿真验证,结果如图8所示。由于在Matlab的Simulink中,模型仿真属于系统验证性质的仿真,并不是RTL级仿真,与目标器件和硬件系统没有关系。因此采用Modelsim对设计电路进行功能仿真。Modelsim是Mentor公司杰出的HDL仿真工具,以其强大的数字和模拟仿真功能而广泛应用,且仿真结果直观、易懂,如图9所示。

2.3 系统硬件验证

通过SignaICompiler把设计模型文件转成相应的硬件描述语言VHDL设计文件。在QuartusⅡ集成环境中,对.vhd文件进行编译、时序仿真,对设计文件进行仿真验证,确定DE2开发板中PIO所对应的输入/输出即引脚锁定;对器件编程并最终下载到目标芯片DE2EP2C35F672C6上,以实现硬件测试;调用Signal-TapⅡ观察硬件测试结果,经D/A转换由示波器观察波形输出,其结果与系统仿真结果相同,从而验证了系统设计的合理性。

3 结 语

从工程应用的角度,提出了基于DSP及SOPC的结构化、模块化设计方法,该方法可以推广到其他电子设计领域,使系统电路设计更加简便直观,且便于扩展,具有较高的实用性和可靠性。通过对比DSP和SOPC设计的优缺点表明,与DSP设计相比,SOPC技术可以大大缩短系统的设计周期,节省设计费用,提高产品的性价比和竞争力,因此更具有良好的推广和应用前景。(编辑:chiying)

- 单片DSP处理器功能系统的SOPC技术设计(01-12)

- 基于Linux的SoPC应用系统设计(04-23)

- 基于DSP的实时数据处理系统浅析(02-28)

- 基于LXI总线的1553B通讯模块设计与开发(11-24)

- 双MicroBlaze软核处理器的SOPC系统设计(01-27)

- 基于Nios II的RTEMS嵌入式开发模式的搭建(03-01)