硬盘驱动器接口技术与嵌入式应用整合方案

通常,硬盘驱动器并不需要支持所有的模式。目前,1.8英寸硬盘能够支持所有的模式,1英寸硬盘能支持到UDMA4模式。考虑到便携消费类市场对尺寸和功耗的要求,因此本文侧重于讨论1.8英寸或更小尺寸的硬盘驱动器。这些微硬盘的实际数据吞吐量远小于他们的理论值。硬盘的直径直接影响了数据传输率。例如,1英寸硬盘驱动器比2.5英寸硬盘驱动器要慢许多,这是因为硬盘外直径变小,意味着外围磁轨的最快线速度也将同样变小。

|

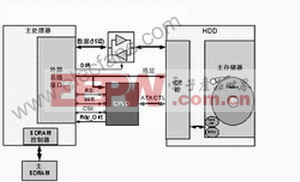

图1主ATA控制与CPLD解决方案:采用一个外部总线接口或GPIO端口和一个用于连接逻辑电路的CPLD,主CPU控制ATA时序和与硬盘相关的任务。

目前,大多数便携式低功耗嵌入式处理器都支持CF接口,但是缺乏专用的IDE控制器。虽然CF3.0支持真IDE模式和ATA规范的部分标准,但是这种方法必须依靠处理器本身来控制ATA时序和建立数据连接。而且从系统角度来看,这种模式在传输大量数据时效率不高。在嵌入式领域,当设计师采用硬盘驱动器技术时,可以选用CF接口、通用I/O端口或者一个带有用于连接某些逻辑电路的CPLD的外部总线接口等方案来实现连接。这使得他们可以采用现有的主处理器架构和软件环境来更快地推出产品,取得市场先机。尽管这种方法简单且经济,但在采用这种方法前,设计师必须充分理解它对系统性能的影响。因此,在选择一个特定的系统方案之前,有必要为终端应用确定一个清晰的、可量化的性能目标。因为只有这样,才能够应用该目标来指导系统划分过程和决定是否有必要改善性能。

|

图2 局部总线接口和QuickLogic IDE控制:采用一个外部总线接口或GPIO端口和外部硬件中的专用QuickLogic IDE控制器来加速对硬盘驱动器(HDD)的读写。

外部总线接口与CPLD

优点

本方案只需要控制信号和主处理器的部分寻址信号与CPLD连接,来产生硬盘驱动器所需的接口信号。当系统中存在其他设备共享数据总线时,还需要额外的分离逻辑部件将总线与系统的其他部分分离开来。从硬件角度来讲,这个方案非常简单、直接而且提供了应用所需的存储。然而,系统设计是需要考虑数据吞吐量的可能瓶颈和对主处理器的影响。若要设计一个性价比高和有竞争力的解决方案,需要满足以下两条件中至少一个:硬盘读写的数据中不包括极大数量的数据文件或丰富的多媒体内容;性能和数据吞吐量不是系统的关键性要求。

缺点

当处理器负责产生和控制ATA时序的时候,它将浪费额外的周期来处理时序和数据移动。系统中,性能瓶颈的多少取决于是否存在DMA控制器,以及主处理器在外部总线接口和主内存之间的数据传输效率。如果再加上微处理器在每次数据读写中对来自硬盘驱动器的IO-RDY信号反应的等待时间,将形成一个很严重的性能瓶颈。由于本方案直接与每个驱动器相关的任务挂钩,因此对CPU占用率产生了很大的影响。主CPU的绝大多数时间将被用来为硬盘服务,而不是执行与应用相关的任务。实际应用中,数据传输的最大速率请参见表1。

外部总线接口和QuickLogic IDE控制器

优点

本方案通过在硬件中增加一个外部IDE控制器,来加速硬盘驱动器数据传输和读写控制,从而降低了流程中主处理器的负载。在本方案中,只有主处理器的本地存储器总线连接到IDE桥接设备。外部IDE控制器拥有一片用于数据双向传输缓冲的容量为512字节的嵌入式内存。缓冲内存使得主处理器实现了直接在512字节扇区内执行读写操作而不必等待中断或外部连接IDE设备的准备。在等待中断信号或者IDE控制器发送的512字节扇区数据准备完毕信号的同时,主处理器可以不间断地运行其他任务。

在数据扇区准备好后,再调用中断机制,这使得系统可以实现比轮流检测机制更好的性能。与中断机制不同,轮流检测在增加了软件投入的同时也降低了系统的性能。

如果在CPU中,存在供外部设备使用的DMA控制器,通过对主内存数据扇区的DMA操作,可以进一步提升系统性能。由于硬盘消耗大量的静态电流,因此微瓦FPGA能够关闭硬盘的电源来降低不读取数据时硬盘的功耗。同样的机理也被iPOD所采用。使用微瓦FPGA来控制硬盘功耗的主要优点是,可以在数据传输完成以后,

应用 整合 方案 嵌入式 技术 驱动器 接口 硬盘 相关文章:

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- SHARC引领第四代通用DSP高端应用潮流(09-27)

- 在应用可编程测控网络设计(03-15)

- 基于dsPIC33F系列单片机的应用程序升级方法(04-03)

- 采用混合时钟模式提高Linux时钟精度的方法(05-10)

- MSP430低功耗原理及其在海温测量中的应用(06-06)