基于Xilinx 和FPGA的DDR2 SDRAM存储器接口控制器的设计

,设计人员可再次进行仿真,以验证整体设计的功能。MIG 工具还可生成具有存储器校验功能的可综合测试平台。该测试平台是一个设计示例,用于Xilinx 基础设计的功能仿真和硬件验证。测试平台向存储控制器发出一系列写和读回命令。它还可以用作模板,来生成自定义的测试平台。

设计的最后阶段是把 MIG 文件导入 ISE 项目,将它们与其余 FPGA 设计文件合并,然后进行综合、布局和布线,必要时还运行其他时序仿真,并最终进行硬件验证。MIG软件工具还会生成一个批处理文件,包括相应的综合、映射以及布局和布线选项,以帮助优化生成最终的 bit 文件。

高性能系统设计

实现高性能存储器接口远远不止实现 FPGA 片上设计,它需要解决一系列芯片到芯片的难题,例如对信号完整性的要求和电路板设计方面的挑战。

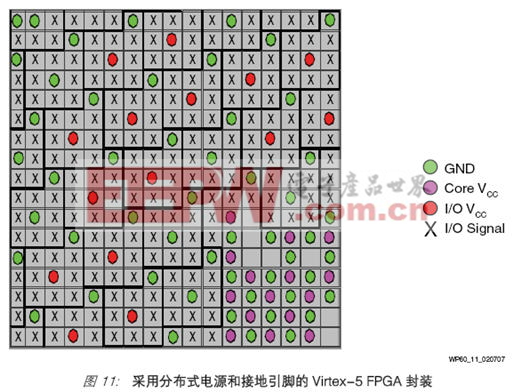

信号完整性的挑战在于控制串扰、地弹、振铃、噪声容限、阻抗匹配和去耦合,从而确保可靠的信号有效窗口。Virtex-4 和 Virtex-5 FPGA 所采用的列式架构能使 I/O、时钟、电源和接地引脚部署在芯片的任何位置,而不光是沿着外围排列。此架构缓解了与 I/O 和阵列依赖性、电源和接地分布、硬 IP 扩展有关的问题。此外,Virtex-4 和Virtex-5 FPGA 中所使用的稀疏锯齿形封装技术能对整个封装中的电源和接地引脚进行均匀分配。这些封装提供了更好的抗串扰能力,使高性能设计中的信号完整性得以改善。图11 所示为 Virtex-5 FPGA 封装管脚。圆点表示电源和接地引脚,叉号表示用户可用的引脚;在这样的布局中,I/O 信号由足够的电源和接地引脚环绕,能确保有效屏蔽 SSO 噪音。

对于高性能存储器系统来说,增加数据速率并不总能满足需求;要达到希望的带宽,就需要有更宽的数据总线。今天,144 或 288 位的接口已经随处可见。多位同时切换可导致信号完整性问题。对 SSO 的限制由器件供应商标明,它代表器件中用户可为每组同时使用的信号引脚的数量。凭借稀疏锯齿形封装技术良好的 SSO 噪音屏蔽优势和同质的 I/O 结构,宽数据总线接口完全可能实现。

表1 列出了 Virtex-5 LX 器件和满足 600 Mb/s 数据速率下的 SSO 需求的最大数据总线宽度。

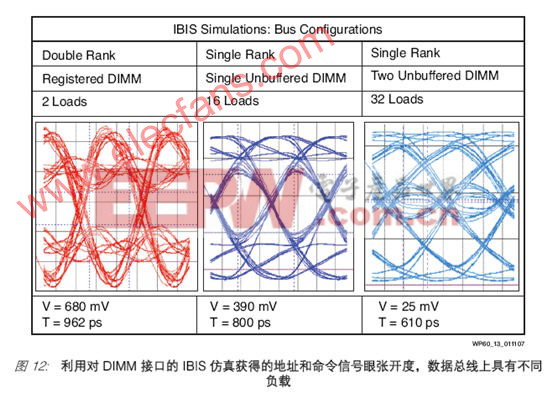

设计大容量或密集型存储器系统的另一个挑战是容量负载。高性能存储器系统可能需要由地址和命令信号共用的一条总线驱动的多存储器器件。大容量无缓冲 DIMM 接口就是一个例子。如果每个单列 DIMM 拥有 18 个组件,那么包含两个 72 位无缓冲DIMM 的接口可以在地址和命令总线上拥有多达 36 个接收器。由 JEDEC 标准推荐,并在通用系统中常见的最大负载是两个无缓冲 DIMM。总线上所产生的容量负载会极其庞大,导致信号边沿上升和下降需要多于一个时钟周期,从而使存储器器件的建立和保持出错。图12 所示为 IBIS 仿真所提供的眼图,使用的是不同配置:一个寄存DIMM、一个无缓冲 DIMM 和两个单列无缓冲 DIMM。容量负载的范围从使用寄存DIMM 时的 2 个接收器到使用无缓冲 DIMM 时的 36 个接收器不等。

这些眼图清楚地显示了地址总线的容量负载效果;寄存 DIMM 提供地址和命令总线上一个打得很开的有效窗口。一个 DIMM 的眼张开度在 267 MHz 下仍然不错。然而,当负载为 32 时,地址和命令信号有效窗口便大为缩小,而传统的实现方法已不足以可靠地与两个无缓冲 DIMM 接口。

这个简单的测试示例说明负载会导致边沿明显变慢的同时,眼图在更高的频率下闭上。对于总线负载不可减少的系统,降低操作的时钟频率不失为使信号完整性维持在可接受水平上的一种方法。然而,还有其他方法可以在不降低时钟频率的情况下解决容量负载问题:在可以往接口添加一个时钟周期的延迟的应用中,使用寄存 DIMM 可以是不错的选择。这些 DIMM 使用一个寄存器来缓冲地址和命令一类信号,从而降低容量负载。使用基于在地址和命令信号上采用两个时钟周期(称为 2T 时序)的设计技术,地址和命令信号可以用系统时钟频率的一半发送。控制好存储器系统的成本和达到要求的性能一样,也是一个很大的挑战。降低电路板设计的复杂性并减少材料费用的一个方法是使用片上终端而不是电路板上的电阻器。Virtex-4 和 Virtex-5 系列 FPGA 提供一种称为“数控阻抗 (DCI)”的功能,在设计中实现该功能可减少电路板上的电阻器数量。MIG 工具有一个内置选项,允许设计人员在实现存储器接口设计时包含针对地址、控制或数据总线的上述功能。此时要考虑的一个权衡因素是当终端在片上实现时,片上与片外功耗孰优孰劣。

存储器接口的开发板

对参考设计进行硬件验证是确保解决方案严密可靠的重要最终步骤。Xilinx

接口 控制器 设计 存储器 SDRAM Xilinx FPGA DDR2 基于 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)