基于FPGA和VHDL语言的多按键状态识别系统

时间:09-03

来源:互联网

点击:

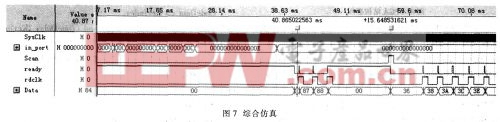

有数据,Ready为低电平;无数据,Ready为高电平。RdClk为读取时钟,相当于确认信号,每读完一个数据,发送一个脉冲。 3.4 FIFORAM模块 与MCU通信的接口种类很多,可选择串口、I2C、并口等形式,应用中可根据MCU资源以及项目成本、进度等具体情况选择最合适的一种方式。该系统设计利用同步FIF0 RAM并口传输。FIF0 RAM模块采用EDA软件库中的标准模块。 4 仿真结果 采用Altera公司提供的Quartus II仿真工具,其集成有与硬件实时操作相吻合的硬件测试工具。综合仿真结果如图7所示,系统时钟SysClk为12 kHz,其仿真结果表明系统设计达到要求。 5 结论 提出基于FPGA器件,VHDL语言描述的特殊键盘设计方案解决远距离、分散、多键动作状态识别问题,极大节省PCB面积和MCU的I/0端口资源。模块中扫描延迟、扫描间隔等参数可根据系统需求灵活改变,FPGA器件使得电路功能的扩展方便,具有极高稳定性和灵活性。这一方案已在实际项目中应用,经现场验证性能稳定可靠。

状态 识别 系统 按键 语言 FPGA VHDL 基于 相关文章:

- 有限状态机的嵌入式Linux按键驱动设计 (11-07)

- 状态机在单片机程序设计中的应用(05-01)

- 基于有限状态机的嵌入式系统模型校验技术(10-14)

- 基于VxWorks的飞机自动化配电的软件设计研究(04-12)

- 嵌入式系统Flash存储管理策略研究(10-19)

- 基于状态机的LCD多级菜单设计(01-23)