一种基于CPLD的声发射信号传输系统设计

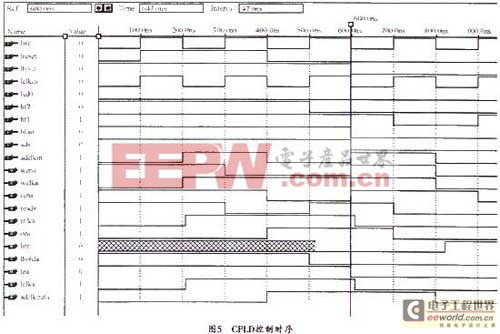

dma读取还未完成,应继续留在s2,如blast为0,则表明此次dma读取完成,可转到s4。s3为单周期写状态,此状态下也要置ready信号为0以表示写数据有效,并在blast为0时转到s4。s4为读写操作完成状态,当lhold被置0时,表明pci9054不再请求本地总线,此时应转到s0,当blast为0且lhold为1时,表明pci9054还要进行数据读写,故应转到s1继续操作。 3.4 控制程序逻辑的仿真结果 max+plusⅱ是开发aletra公司的fpga/CPLD系列产品的软件工具,本设计利用此工具提供的设计环境和设计工具来对cpld控制程序进行开发和调试。其功能时序如图5所示。 cpld的设计是用vhdl编程实现的。本设计的操作代码都已经过仿真,并在实际调试中得到应用。 4 系统驱动程序设计 本设计使用 kdmaadapter类可用于建立一个dma适配器,以标明一个dma通道的特性和提供串行化访问服务;kdmatransfer类则用于控制dma的传输和启动dma传输,以传输dma数据缓冲区物理地址和字节数,dma传输结束后,数据将由公用缓冲区拷贝到应用数据缓冲区;kcommon dmabuffer用于实现公用缓冲区的操作。对于dma操作,本系统还提供了一个特殊的内存,即公用缓冲区。应当说明的是,公用缓冲区是稀有的系统资源,应该避免浪费使用。 5 结束语 本文给出了数据缓存、传输模块控制电路的设计,并采用vhdl语言和cpld很好的完成逻辑控制任务和系统驱动程序的编写与调试。实验结果表明,该数据存储传输模块的硬件、软件工作十分可靠、稳定,可实现640 mbps(80 mbyte/s)以上实时数据的存储与传输,完全能满足声发射信号采集的要求。

driv erworks的driverwizard来创建wdm框架程序。可根据设计需求添加程序代码,从而完成pci设备的dma传输系统驱动程序,以执行dma操作、访问i/o端口和存储器空间、处理器中断和访问pci。根据系统需要,驱动程序的关键是三个方面:硬件访问、中断处理和dma传输。

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)