单片机和CPLD的望远镜伺服控制器设计

摘要:设计基于高速单片机C8051F120和CPLD的高精度大型望远镜的伺服控制器,由单片机实现闭环控制算法、上位机通信和LCD显示控制,CPLD实现增量式编码器计数、电机驱动波形发生以及I/O接口。该控制器可独立进行电机控制,也可配合上位机进行控制,具有实时性和抗干扰能力强、成本低、调试方便等特点。

关键词:C8051F120;CPLD;电机控制;内模控制;LCD

引言

微电子技术和计算机的发展推动着伺服控制技术的进步,控制系统的硬件系统越来越高速化、小型化、模块化,功能也日趋强大完善;而且,伺服控制技术是朝着更开放、更加模块化的控制结构的方向发展的,要求控制器算法实现简单、控制接口灵活,针对不同的伺服控制对象时硬件系统不变,软件系统也可以完成参数的自动调整。

在高精度大型望远镜伺服控制应用场所,采用高精度光电编码器作为主要反馈手段,主要有绝对式和增量式编码器。驱动电机的信号有模拟电压输出或PWM脉冲输出,通过调整电压的大小或PWM的占空比来调整电机的速度。系统具有和上位机的通信接口以及一些逻辑输入/输出接口等。大型望远镜是用于跟踪测量空中飞行目标或观测天体目标的精密光学设备。伺服系统是望远镜的重要组成部分,它对于跟踪目标、精确测量目标的位置以及其他参数都起着重要作用。伺服系统的性能会直接影响望远镜的观测能力,对望远镜的高精度伺服控制需要高精度的位置反馈装置,以及高分辨率的PWM驱动脉冲。

本文采用高速单片机C8051F120作为主控制器,与光电编码器接口多为AB正交码和零位信号输入;驱动电机多采用带死区PWM信号驱动有刷直流电机;采用CPLD实现高速光电编码器的AB码计数、计数位数的设定以及32位的可逆计数,同时可以输出高分辨率的带死区的PWM电机驱动信号。本文结合高速单片机和CPLD的优点进行望远镜伺服系统的控制器设计。

1 系统硬件设计

设计采用高速单片机作为主控制器来构成低成本的伺服控制方案。CPLD具有编程灵活、集成度高、开发周期短、成本低的特点,可实现较大规模的数字电路设计。因此,选择一款合适的CPLD可满足伺服控制系统的AB正交码计数和PWM波形产生等电路接口要求,同时大大减小PCB面积,增强可靠性。整个控制器系统原理框图如图1所示。

作为主控制器的高速单片机选择C8051F120。它是完全集成的混合信号片上系统型芯片,主要实现数学运算、控制算法和A/D采集等功能。

C8051F120具有如下特性:

◆高速、流水线结构的8051兼容的CIP-51内核(100 MIPS或50MIPS);

◆真正12位、100 ksps的ADC,带PGA和8通道模拟多路开关;

◆两个12位DAC,具有可编程数据更新方式;

◆2周期的16×16乘法和累加引擎;

◆128 KB可在系统编程的Flash存储器;

◆8448(8 K+256)字节的片内RAM;

◆可寻址64 KB地址空间的外部数据存储器接口;

◆硬件实现的SPI、SMBus/I2C和2个UART串行接口;

◆5个通用的16位定时器;

◆具有6个捕捉/比较模块的可编程计数器/定时器阵列;

◆片内看门狗定时器、VDD监视器和温度传感器。

CPLD选用A1tera公司的低功耗MAXII系列的EPM570T100。它含有570个逻辑单元(LE),等效于440个宏单元;8192位的用户Flash存储器,可满足用户小容量信息存储要求;最大用户I/0数为76,最短访问时间为4.5ns,内部最大时钟频率为304 MHz,完全满足系统设计要求。EPM570T100主要和C8051F120的P1、P5、P6、P7接口,以及和编码器的ABZ码、8路输出和8路输入接口电路相接,实现和C8051F120的数据总线和地址总线接口电路、外部定时中断电路、译码电路、PWM脉冲发生电路、倍频鉴向电路、计数电路、故障保护电路等功能。

LCD显示模块主要显示系统的状态变量值,如位置、速度、编码器值等信息。采用串口电平转换收发器SP3223实现与上位机的两路RS232通信,可完成工作模式(如定点、等速模式),以及数值大小的设定;同时,单片机可实时地将工作状态变量送至上位机,利于数据记录和分析。控制器参数(如比例系数KP和积分系数KI等)也可由上位机进行设置,对于开放式运动控制模块,这是必需的。

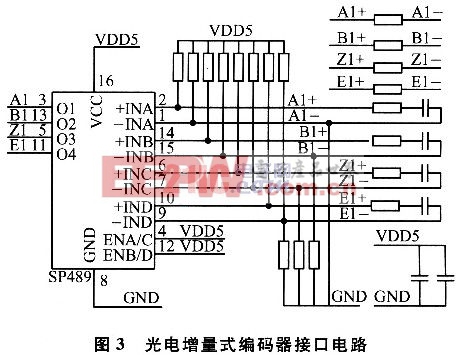

另外,设计了8路按键,用于功能参数设置等。如图2所示。光电增量式编码器的接口一般为RS422差分对输入接口。

如图3所示,光电增量式编码器接口电路具有终端匹配电阻和滤波网络电路,可增强抗干扰能力。其中,接口芯片SP489将RS422信号转换为TTL电平。

2 CPLD片上各模块实现

2.1 倍频鉴向和计数电路

经过图3所示的编码器接口电路处理后,输出TTL电平的A1、B1、Z1信号到CPLD。首先,对波形进行整形、数字滤波处理;经过4细分后,进入辨向电路;然后由可逆计数电路完成对脉冲的计数,输出32位的二进制码值;单片机在每个采样周期中读取计数值来获得位置值,通过微分即可得到速度值。望远镜的位置反馈圆光栅输出的AB码频率可达10MHz,高频CPLDEPM570T100完全可以胜任。在CPLD输入端口进行施密特触发和滤波处理,以避免尖峰毛刺干扰,进一步增强系统鲁棒性。

2.2 时钟电路

CPLD的全局时钟为100MHz,对其进行分频提供给内部各个模块,如计数模块电路、PWM处理电路和单片机的中断信号。100MHz可分频成1kHz、500 Hz、50Hz。本设计中,采样周期为1ms,即1kHz采样频率,用于单片机的外部中断信号。在采样周期内,单片机完成对圆光栅计数采样、速度计算、算法实现、PWM控制变量产生,以及过程状态变量赋值等工作。实际测得完成单个电机控制所需的时间为120μs左右,剩余时间可用于实现LCD显示控制和通信功能。可见,利用该单片机可以胜任望远镜伺服闭环工作。

2.3 PWM脉冲电路

功率级采用H桥电路,需要4路带死区的PWM信号,避免直通。如图4所示,首先由100 MHz产生12.5kHz的三角波信号,与单片机输出的数据(0~8000)进行比较,得到1路PWM信号(数据的大小决定占空比的值,O对应O%,8000对应100%),再由该PWM信号产生与之反向的信号。同时,经死区电路得到2路死区时间至少为5μs的PWM信号,以及经电机工作模式控制电路处理得到的4路驱动功率级PWM信号,可控制电机工作在单极性或双极性方式。当需要控制多个电机时,采用上述方法同样处理就行,这就是CPLD灵活性的具体体现。

- FPGA的DSP性能揭秘(06-16)

- 基于单片机通用引脚的软件UART设计(10-16)

- 分时操作系统思想在单片机中的具体应用 (10-30)

- 基于AT89C51+DSP的双CPU伺服运动控制器的研究(05-26)

- 关于RTX51 TINY的分析与探讨(05-30)

- 基于MC9S12DGl28单片机的智能寻迹车设计(04-03)