基于FPGA的数据采集板设计与实现

时间:12-11

来源:互联网

点击:

0, - 1}为周期循环的两个序列。当外部数据进来时根据不同时刻输出不同的数据, 主要包括原值、原值取反和0。其FPGA实现电路, 如图4所示。

图4 数字混频的FPGA实现电路

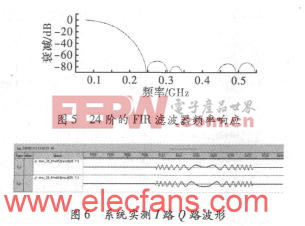

在整个正交相干检波过程中, 除了ADC的量化影响外, 整个正交检波系统的性能, 由低通滤波器的设计决定。由于镜频分量处于滤波器的阻带, 因而阻带衰减决定了镜频的抑制程度。文中采用的低通滤波器为24阶F IR滤波器, 其阻带衰减> 70 dB镜频分量得到了较好的抑制 。24阶FIR滤波器的频率特性, 如图5所示。

输入时宽带宽积为55的线性调频信号, 实测的I路与Q路波形, 如图6所示。

把实测数据导到Matlab进行分析, 得到镜频抑制比满足系统的要求, 如图7所示。

图7 系统实测数据, 低通滤波法频率归一化后的镜频抑制比数据采集板实物图, 如图8所示。

3 结束语

文中设计的基于CPCI总线的数据采集板, 8路信号同时采集并处理, 兼备强大的数据处理能力和高实时性。整个系统实现的是数字正交采样, 无论是中频采样, 还是数字下变频, 都有一定的通用性, 在以后类似的应用中, 无需重新设计, 只需通过资源分配和算法的再实现, 足以达到预期的效果, 保证可靠性的同时也大大的缩短了研制周期。

图8 数据采集板实物图

实时性。整个系统实现的是数字正交采样, 无论是中频采样, 还是数字下变频, 都有一定的通用性, 在以后类似的应用中, 无需重新设计, 只需通过资源分配和算法的再实现, 足以达到预期的效果, 保证可靠性的同时也大大的缩短了研制周期。

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)