ARM设计的FPGA可重构配置方法的实现及应用

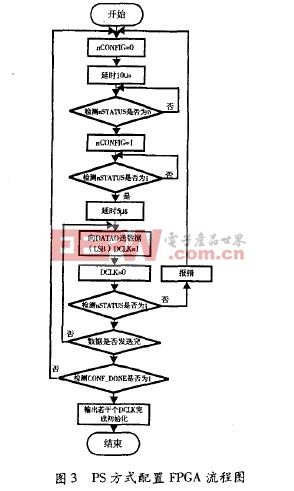

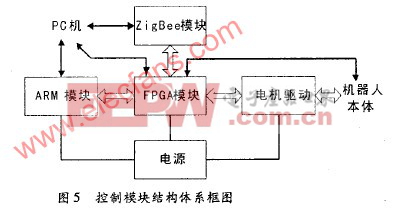

状态,当ncONFIG变为高电平时,FPGA退出复位状态,释放漏级开路的nSTATUS管脚,nSTATuS在外部需要被l0 K的上拉电阻拉高,nSTATUS管脚变为高电平后,FPGA即进人配置阶段,此时,FPGA已做好了接收配置数据的准备. FPGA的nsTATuS管脚变高后,延时5 s左右,在DCLK的上升沿FPGA即可从DA L0管脚串行的接收配置数据,配置数据按低位在先高位在后的顺序从数据线上送出.当所有数据都接收完后释放漏级开路的CONFIG— DONE管脚,CONFIG—DONE管脚在外部需要被10 K的上拉电阻拉高,CONFIG—DONE管脚由低到高的跳变表明配置阶段结束,FPGA进入初始化阶段.如果在配置过程中出现错误,则n rATuS管脚将输出低电平,FPGA在内部自动复位,处理器可以通过查询ns1IATuS管脚状态判断在配置过程中是否有错误发生,如果nsTATuS管脚在配置过程中变低则表明有错误发生,如果在软件中设置了错误发生后自动重新开始配置选项则FPcA会延时一段时间后释放nsTATuS,此时nsTATuS被外部上拉电阻拉高,CPu在nsTA—Tus上检测到一个由低到高的跳变后重新开始配置.若软件中未设置“错误发生后自动重新开始配置”选项则需要CPu首先将nCONFIC管脚置低再拉高以开始重新配置. 在初始化阶段,初始化时钟可以是FPGA内部时钟或外部由CLKusR管脚提供的时钟,本例使用了FPGA内部时钟,FPGA将为初始化提供时钟,这样,初始化阶段不再需要外部时钟.初始化阶段完成后INIT—DONE管脚变为高电平,指示FPGA成功进人用户模式,配置过程结束.需要注意的是,若此时CONF—DONE或INIT_DONE未变为高电平,则表明此次配置过程不成功,需要cPu重新进行配置. 2.2 配置程序设计 下面是完整的重构程序及流程图(图3所示),作为s3c24lOx ARM处理器 μC/OS—II实时操作系统的一个任务运行,但在工程应用中要结合实际情况做适当修改. 基于μC/OS—II配置程序: U8Fpga~DownLoad(v0id) {U8 Bootaddr; U32 CountNum =O柏: u8 FpgaBu如; U16 i: Bo0taddT:(u8 )(O】(33ooooo0);/ 配置数据起始地址 / SeI— Datao(O); seLnCONFIG(0);/_将ncONFIG置低电平 / set— DCLK(O); hude1ay(10);/}延时1O / if(Re们一nSTATUS) {prin (”err0r:nSTATuSis 1 1”); retum O;} Set— nC0NFIG(1); while(!Read—nsTATUS); hudelay(5); p nd(”十co gIlre FPGA.-); while(c0untNum =O)(24294)/}串行配置数据 / {FpgaBu任er= (Bo0t&ddT+c0un um); if(!(CountNum%1O24))pdnd(”.”); f0r(._O;i8;i++) {Set—Data0(FpgaBu丘 脚 1); hudelay(1); seLDCLK(O); FpgaBu艉r> > = 1; if(!ReaⅡ一ns1、ATUS) { nEf(”\n、卜C0 gure Error:nsTATus is 0 1、n ); ren】m O;} Set— DCLK(1); } C0untNum + + : } SeI— Datao(O); S eI— DCLK(O); if(!Reau—nsTATuS) {p ntf(”、n\r—Configure Ermr:nsrATus is O!、n、r ); retum O;}} else if(Read—nC0NF—Done) {p ntf(”\n\卜-Co gure success! 、n );} fnr(i=O;i(5O;i++)/ 初始化 / {Set—DcLK(1); hudeIay(1); Set— DCLK(O); hude1.dy(1);} 、 if(!Read—nC0NF—D0ne) {printf(”、r\n—configure En r:nCO F—Done is 0 1”); retum 0:} retum l: { 3 可重构配置应用 结合上述可重构配置分析,我们利用了FPGA可重构特性,实现模块化机器人控制器的设计.模块化机器人结构复杂,控制电机数量多,而且针对不同构形控制策略也有差别,如四自由度串联式机器手构形和全向移动小车构形(图4所示)从控制策略到控制电机数量都有很大的不同,这就要求控制器可以根据不同构形动态的改变控制策略,也即控制器的可重构.为此,在模块化机器人可重构控制模块结构设计中,提出基于ARM和FPGA的动态可重构的模块化机器人控制系统方案,充分利用嵌入式ARM核微处理器高性能、低功耗、资源丰富等方面的性能和FPGA内部逻辑可重构的特性,由主处理器根据机器人当前构形选择不同的控制策略并对FPGA内部逻辑进行动态重配,以适应不同构形及应用的需要.结构设计框图如图5所示。 ARM模块选用s3c241Ox运行 C/OS—II实时操作系统,负责运行控制软件,完成模块化机器人运动规划,实时监控系统运行状态,实现人机交互功能及对FPGA内部逻辑实时重构.FPGA内部运行软核处理器,负责与模块化机器人运动控

方法 实现 应用 配置 重构 设计 FPGA ARM 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 专家指导:Linux操作系统密码恢复方法(05-16)

- 基于多核DSP Bootload代码加载方法研究(01-16)

- 基于DSP 的大容量无线传输技术中高性能的启动方法(03-16)

- 多核调试新方法探讨(10-22)

- 有备无患Linux操作系统备份方法介绍(06-06)