基于PSoC 的嵌入式数字滤波技术

在定义关系密切的 PSoC3 和 PSoC5 系列产品时,赛普拉斯的架构师决定不再在竞争激烈的市场中仅仅提供一款同质化的产品。不管采取什么架构,硬件的功能都应重点用于高效地实现有用的工作目的。我们希望 PSoC 真正成为片上可编程解决方案,能够解决实际客户遇到的实际问题。

为了给新一代 PSoC 器件提供更强的解决问题的功能,我们采用了一系列独特的外设和信号处理块,既有模拟的,也有数字的。本文将重点讨论这些大幅简化采集信号数字滤波工作的信号处理块,并讨论该技术已经在其中证明自身实力的一些应用。

嵌入式数字滤波的架构增强

首先,我们为什么希望使用嵌入式滤波器而不是将信号处理指令集成到普通的微控制器中呢?究其原因就是项目设计层面和系统集成层面的分区问题。在项目开发过程中,项目的规模、目标和整体架构经常发生变化。单核单片式编码项目要想跟上这种变化的速度,着实是一个挑战,尤其是目前的项目常常是由非集中化的多个不同设计团队一起完成的,这更增加了相关的难度。在块层所使用的功能元件中嵌入信号处理,能确保项目管理在元件设计层面实现分支,同时也能确保在算法改变时,信号处理负载发生的差异不会影响通信管理等时间关键性任务。

数字滤波器块 (DFB) 是首款PSoC3 和 PSoC5 系列产品中支持嵌入式数字滤波的硬件元素,这是一款连接于外设总线的小型数字滤波器引擎。实际上,它是存储器、MAC、ALU 和微代码控制库的紧密组合,其 VLIW 架构能支持不同的操作,如 24 位 x 24 位到 48 位乘法和加法等能以系统时钟速率并行执行,在 PSoC3 中的频率可高达 67MHz,而在 PSoC5 中的频率则可达 80MHz。数据和系数存储在一对专门的本地 128x24 位存储器中,并能在整个系统总线上进行存取。许多滤波拓扑都能在这一结构上高效编码。

配合嵌入式数字滤波应用 DFB 的是通用数字块 (UDB) 阵列。它在多功能架构中结合了 PLD 和数据路径/ALU块,既能用于数字数据源集和汇集连接,也能用于高时钟速率重复结构,如级联积分器/梳状滤波器 (CIC) 和噪声成形数字转换器。

在 PSoC3 和 PSoC5 系统中如何使用嵌入式数字滤波

数字滤波器块可通过几种方式使用。PSoC Creator 中集成的滤波器设计工具支持拖放工作方式,将数字滤波包括到信号流程中来。启动时 PSoC Creator 配套提供了专用的 FIR 滤波器“组件”,在系统中可以像其他块一样使用。该组件能对信号应用多种不同滤波器,既能单独使用,也能组合使用。图 1 显示了该组件的屏幕截图,从中我们看出它在 PSoC Creator 项目中的使用情况以及设置属性的配置窗口。今后,更多滤波器拓扑和互动滤波器设计向导还将添加到 PSoC Creator中。

图 1:PSoC Creator 中的标准 FIR 滤波器组件

与第一代 PSoC 产品一样,我们的客户和我们自己的系统工程师一直期待着全新 PSoC3和 PSoC5 应用的到来。PSoC 的核心理念一直是推出灵活的产品,支持在产品设计时还暂未设想到的全新应用。这种灵活性同样适用于数字滤波器块等功能块。我们已经用该块开发了几款定制应用,并作为组件实施于 PSoC Creator 原理图中。由于信号处理与主 CPU 相分离,我们能通过一系列 Creator 组件实现 IP 的重复使用,而全部设计人员都能共享这些组件。

使用 PSoC3/5 的高性能嵌入式滤波示例

“时间校正”滤波器——多相内插

如果用 PSoC3 来满足近期电表读取应用的概念设计要求,我们需要补偿单 Δ-Σ ADC 的通道间计时偏置,满足多相电压和电流多路复用的要求。如果不纠正上述时差的话,系统准确性就会在加载低功耗因数期间快速下降,而且在线路频率高谐波的功耗估算也会出问题。

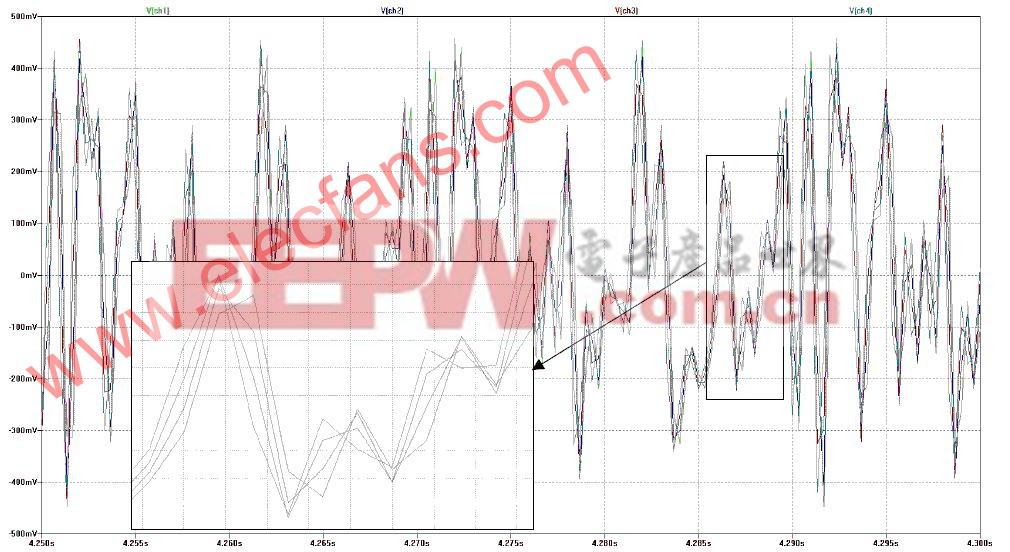

数字滤波器块非常适用于 FIR 滤波器,我们用它来创建多相内插滤波器。在我们的原型设计中共有四个通道,每个通道有 20 个抽头 (tap)。该滤波器从单 ADC 获得多路复用的数据流,将其“解包”为四个新的数据流,上述解包通道的信号延迟有差别,就好像信号同时被四个采样 ADC 捕获一样,需要对采样时间进行校正。图 2 显示了四输入多路复用转换器顺序采样相同(带限)信号所得的四个数据集。

图 2:ADC 的四个顺序多路复用输入获得相同的信号……

图 3 显示了内插滤波器系统的四个输出,我们看到底层带限波形在形状和计时方面都已经得到了准确重构。这种方法使单个高品质 ADC 能满足极高的计量准确性要求,支持各种相关功率因数和谐波频率要求。这种方法对其他需要高效同时采样的应用而言同样适用。

图 3:……

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 用8位微处理器实现数字低通滤波器设计(05-15)

- 基于LabVIEW的DSP设计(04-10)

- 仪器和测量技术中的DSP(08-07)

- DSP滤波器用于扩展数字化仪器的性能(01-25)

- 基于DSP的低功耗接收机单边带解调方法(01-10)