基于VRS51L3074的多点定闹电子日历钟的设计

摘要 论述了多点定闹电子日历钟系统的设计,在VRS51L3074单片机的控制下,使用串行时钟芯片DSl2887,实现时间和闹钟的设置功能。通过键盘和液晶显示提示,可以方便地校对时钟和设置闹钟,利用键盘、LCD显示模块构成人机交互界面,实现时间和日历显示及设置多个闹点等。此种电子钟的特点是操作方便、工作可靠、具有一定的实用价值。

关键词 单片机VRS51L3074;多点定闹;DSl2887;LCD显示

文中是以Versa 8051系列MCU的典型器件VRS51L3074和时钟日历芯片DSl2887为核心制作的可多定点电子日历时钟。该系统功能齐全,可存储多个闹点,采用液晶显示器件LCD以清晰完美的视觉效果显示出时间、日历等各种信息,有操作简单、工作稳定、功耗低、使用方便等特点。

1 方案论述

VRS51L307是美国Ramtron公司最新推出的8 kBFRAM铁电存储器的8051单片机。该单片机将外围功能模块和40 MI/s(兆指令/秒)单周期8051内核集成在一起,工作电压3.0~3.6 V,有精确的内部振荡器。

本系统采用VRS51L3074单片机作为控制核心,使用单片集成的即时时钟芯片DSl2887来实现时钟功能,显示系统采用液晶模块LCD显示时间、日历及闹铃等提示信息,有着智能化的人机界面。用此方案设计的电路图简单,不需要驱动电路,用并行口的数据线便可以实现时间、日历以及闹钟的显示。 VRS51L3074有成熟的闪存技术,本身自带有看门狗定时器电路,这样在单片机死机或遇到程序故障时系统能够自动复位,看门狗定时器由一个14位预分频器构成,以系统时钟或者是系统时钟的分频信号作为其计数源,当看门狗溢出时将使系统复位。系统时钟频率可动态调节,有集成省电、上电复位/掉电检测等功能。

2 系统基本原理

用VRS51L3074控制功能将即时时钟DSl2887的年、月、日、星期、时、分、秒等信息并行输入LCD液晶显示器上,时间和日历还有闹钟的调整则通过键盘的控制功能将各种调整信息反映到单片机中,并通过单片机的并口将各种时间、日历和闹钟信息输入给LCD液晶显示器,从而实现整个设计的控制功能。

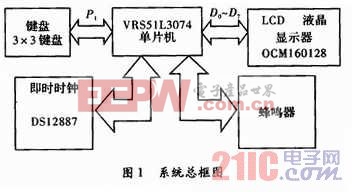

本系统对外围器件的访问都是通过I/O方式,其中单片机的P1口与键盘连接,P0口的8个端口用作单片机的数据线分别与显示器和即时时钟相连,P60和 P27分别用作控制端,用来控制单片机与LCD显示器以及单片机与即时时钟之间的数据传输;本系统中,由于采用LCD显示屏作为显示系统,因而用键盘作为控制系统对于便携式的日历钟来说,有利于操作和控制。在本设计中,各功能键的控制通过软件编程的方法来实现,这样利用键盘的不同功能键就可以实现对闹钟、时钟和日历的调整控制。整个设计的系统图,如图1所示。

3 系统硬件设计

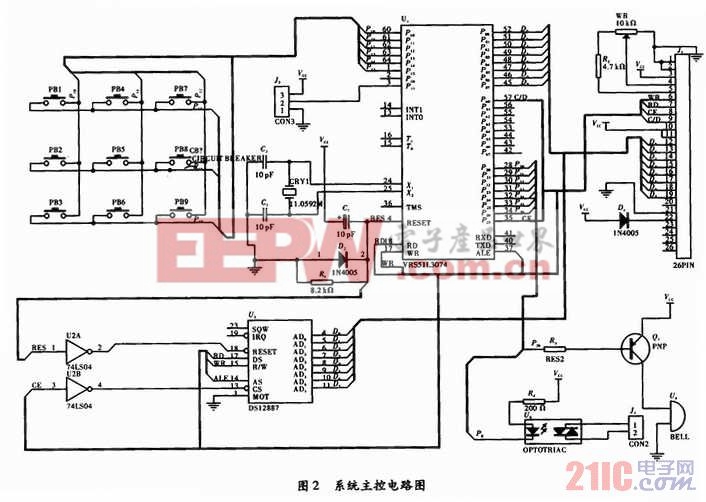

硬件系统由单片机及其键盘电路、时钟系统、闹点报警功能和LCD显示部分组成。整个系统的电路设计以单片机VRS51L3074和时钟芯片DSl2887的设计为核心,外加液晶显示器OCM160128-I(内置T6963C控制器),蜂鸣器以及键盘。

采用VRS51L3074单片机作为控制核心对时钟芯片DSl2887进行控制,读取时间,提取数据,对输入信号进行处理,最后通过LCD显示各种时间、日历及闹钟信息,从而实现整个设计的控制功能。系统主控电路如图2所示。VRS51L3074片内自带40 MHz振荡器,可无需外部晶振为系统提供时钟信号。通过对时钟主电路之间预分频器的配置可灵活设置系统时钟以满足不同应用的需要。系统时钟源选择及分频比设置由特殊功能寄存器DEVCLKCFGl和DEVCLKCFG2控制。

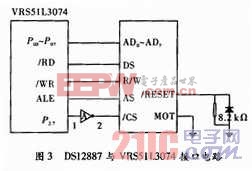

3.1 单片机与DSl2887时钟芯片的接口设计界面

单片机与DSl2887时钟芯片的接口界面如图3所示。两者之间要实现同步通信,就需要用到6个口线:(1)复位/RESET。(2)I/O数据线。(3)片选信号线/CS。(4)数据激发或读取线DS。(5)读取/写入,输入线R/W。(6)地址激发输入线AS。

在以上6个口线中,DS、R/W都有两种操作模式。本设计采用Intel总线时序,故MOT脚接地。在这种模式下,DS(数据激发或读取)脚称为/RD 脚。AD0~AD7是多工双向的地址/数据总线。在总线周期的第一段时间呈现的是地址,同样的IC脚和信号路径,在第二段时间当成数据使用。因总线从地址到数据的改变是发生在内部SRAM的存取时间,所以地址/数据作成多工形态并不会使DSl2887的存取时间变慢。片选信号线/CS选择输入为LOW时,即可对DSl2887进行存取,在总线周期即使没有使能/CS脚,也同样会锁存住地址但没有存取的动作发生。当Vcc 4.25 V时,DSl2887会除能/CS脚,禁止存取动作,此功能会保护在电源消失期间的即时时钟和SRAM里的数据。地址激发输入AS送一个正向地址激发脉冲到输入脚,然后在A

MCU 相关文章:

- 如何将DSP和MCU两者完美结合(08-10)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 微控制器省电管理方法(05-04)

- 利用低成本的MCU的UART驱动智能卡(05-04)

- DSP结构特点和运算性能(07-19)

- 基于DSP+MCU的列车滚动轴承故障诊断系统设计与应用(10-08)