基于AT89S52和K9F6408U0A的语音数字系统设计

数据采集技术涉及领域广,采集信号的动态范围宽,处理数据量大,对系统实时性能要求高。以数字信号的形式对信号进行处理,具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,满足了对信号快速、精确、实时处理及控制的要求。本设计利用了数字电路的这些优点,对传统的模拟录音电路进行了改进,以较低的成本使性能得到了提高。

1 方案论证

本设计以数字化信号的形式对音频信号进行处理,有以下3种方案可供选择:

1)直接利用语音芯片进行语音录放。Winbond公司的ISD系列语音芯片采用了Chip-Corded专利技术,声音无需A/D转换和压缩就可直接存储,不存在A/D转换误差,在一个记录位(BIT)可存储多达250级声音信号,相当于通常A/D技术记录容量的8倍。片内集成了晶体振荡器、麦克风前置放大器、自动增益控制、抗混叠滤波器、平滑滤波器、声音功率放大器等,只需很少的外围器件,就可构成一个完整的声音录放系统。

2)利用DSP对采样信号进行处理。DSP是专门为快速实现各种信号处理算法而设计的、具有特殊结构的微处理器,其处理速度远远超过一般的CPU。

3)利用AT89S52作为系统主控芯片,利用ADC0809对音频信号进行采集和A/D转换,将转换得到的数字化音频信号存储到扩展的数据存储器中,利用软件对信号进行数字滤波,最后通过单片机输出PWM信号来完成放音。

从经济和技术等因素考虑对上述3种方案进行比较:直接利用语音芯片可以减少很多外围电路,电路设计方便,但语音芯片使用不够灵活。DSP具有强大的数字信号处理功能,使用灵活,但该芯片价格较高,不适于一般的应用。方案3)中器件均为常用芯片,易于获取,且价位不高。因此,方案3)为最佳设计方案。

2 硬件设计

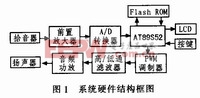

图1为系统硬件结构图。音频信号通过拾音器将声音信号转换为可以处理的电信号,前置放大电路用来对拾音器的输出进行放大,与A/D转换电路匹配,A/D转换电路实现对模拟信号的编码。微处理器是系统的核心,它用来对数字化音频信号进行处理和存储,协调系统各个部分的工作,输出PWM波来驱动输出电路。

2.1 单片机

单片机是系统的控制中心,它主要实现以下的功能:控制LCD显示语音信号的相关信息,控制按键识别和功能选择;控制音频数据的采集并存储在Flash ROM,放音时读取Flash ROM中数据,用软件方法产生PWM脉冲信号,实现语音的存储和回放。

2.2 声音信号拾取、放大电路

声音信号拾取电路就是将声音信号转换为电信号的装置。本设计选用麦克风,它是一种声敏电阻,其阻值随外界声音信号的变化而变化,将其串联在电路中,电阻的变化形成电压的变化,经过电容通交隔直,就得到了表征声音信号特征的电信号。

然而由于声音信号拾取电路输出电压的幅值很小,为20~25 mV,若将该信号直接与A/D转换电路相连,由于A/D转换器最小分辨电压也为毫伏数量级,会产生很大的误差,为了保证系统的精度,在和A/D转换电路相连之前,需串联一个放大电路,考虑到声音信号拾取电路的输出信号很小,放大电路的失真度和噪声对系统的精度影响最大,故将其设计为抗共模干扰强的并联负反馈放大电路,由于音频信号的频宽较大,故选用宽频带,低输出阻抗的双运放NE5532。

2.3 A/D转换电路

A/D转换电路由A/D转换器ADC0809与系统处理器AT89S52组成,主要实现对放大后的声音信号进行采样。ADC0809与AT89S52的电路连接如图2所示。

从图2中可以看到,把ADC0809的ALE信号与START信号接在一起,这样可使得在信号的前沿写入(锁存)通道地址,紧接着在其后沿就启动转换。启动A/D转换只需要一条P2.7=0指令。在此之前,要将P2.7清零并将最低3位与所选的通道对应的地址送入数据指针DPTR中。ADC0 809的转换结束信号EOC取反后与AT89S52的![]() 相连,采用中断方式读取A/D转换结果,并启动下一次A/D转换。也可定时启动A/D转换,并读取上次转换结果。

相连,采用中断方式读取A/D转换结果,并启动下一次A/D转换。也可定时启动A/D转换,并读取上次转换结果。

2.4 声音编码存储电路

在采样时每一采样点都会产生1字节的数字编码信号,由于采样的频率为8 kHz,若录音15 min,则所需的存储空间为7.031 25 MB,故系统选用8 MB的Flash存储器K9F6408U0A,由于该存储器的地址线和数据线可复用,这样可节省I/O接口。K9F6408UOA的最大优点在于其命令、数据和地址均可通过8条I/O接口线与主控制器进行通信,大大简化了系统的连线,增强了系统的稳定性。除8条I/O接口线外,K9F6408 UOA还包括以下控制线,1)CLE:命令锁存使能端,高电平有效。在![]() 信号的上升沿,命令信号可通过I/O口锁入命令寄存器;2)ALE:地址锁存使能端,高电平有效。在

信号的上升沿,命令信号可通过I/O口锁入命令寄存器;2)ALE:地址锁存使能端,高电平有效。在![]() 信号的上升沿,地址信号可通过I/O口锁入地址寄存器;3)

信号的上升沿,地址信号可通过I/O口锁入地址寄存器;3)![]() :片选线,低电平有效。在页编程或块擦除操作期间或器件处于忙状态时,

:片选线,低电平有效。在页编程或块擦除操作期间或器件处于忙状态时,![]() 高电平将被忽略。4)

高电平将被忽略。4)![]() :写使能口,命令、地址和数据在

:写使能口,命令、地址和数据在![]() 信号的上升沿被锁定;5)

信号的上升沿被锁定;5)![]() :读使能口,在该口的下降沿将数据送到I/0口线上,并使内部列地址寄存器加1;6)WP:写保护口,低电平有效,当其为低时,编程擦除操作禁止;7)R/B:操作状态指示信号。为低时,表示正在编程、擦除或读操作,操作结束后变高。利用上述控制线,从而方便实现系统主控制器对K9F6 408U0A的控制。AT89S52单片机与K9F6408UOA存储接口电路如图3所示。

:读使能口,在该口的下降沿将数据送到I/0口线上,并使内部列地址寄存器加1;6)WP:写保护口,低电平有效,当其为低时,编程擦除操作禁止;7)R/B:操作状态指示信号。为低时,表示正在编程、擦除或读操作,操作结束后变高。利用上述控制线,从而方便实现系统主控制器对K9F6 408U0A的控制。AT89S52单片机与K9F6408UOA存储接口电路如图3所示。

音频 AT89S52 K9F6408U0A 闪速存储器 PWM A D转换器 定时中断 相关文章:

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于DSP的广播级数字音频延时器(06-07)

- TMS320C6727的音频采集处理回放系统设计(01-05)

- 朗谷数字音频处理技术在音频及网络通讯领域的应用(05-19)

- 带DSP功能的超低功率音频编解码器帮助解决音频方案挑战(05-04)

- 基于S3C4480X控制的蓝牙音频网关设计与实现(07-12)