基于DAS AD7606的可扩展多通道同步采样数据采集系统(DAS)的布局

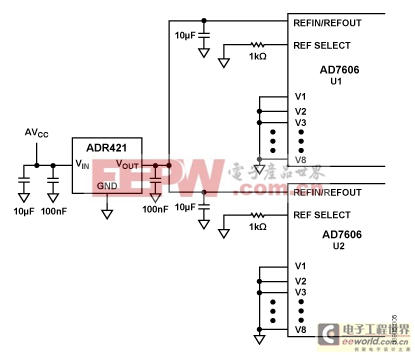

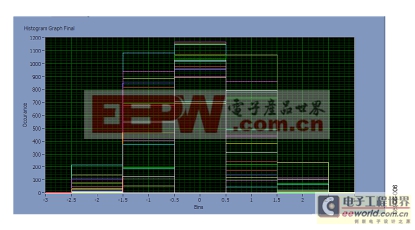

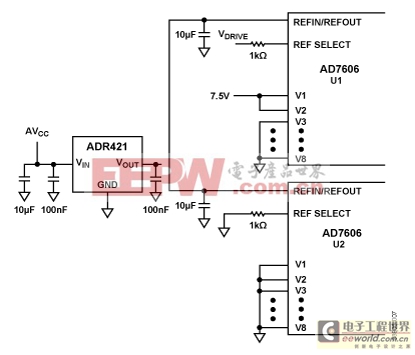

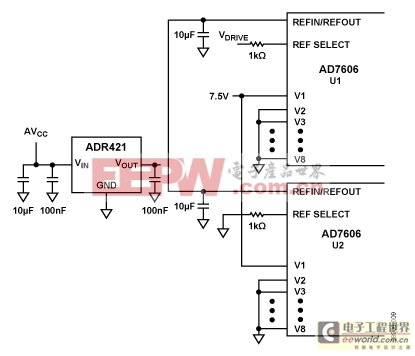

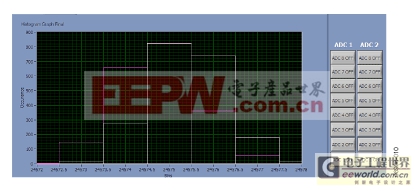

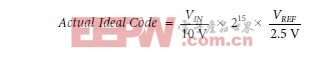

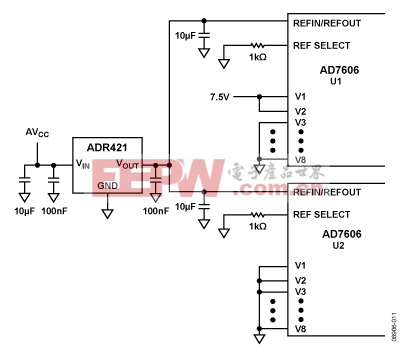

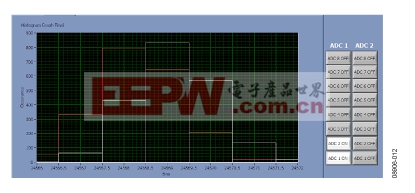

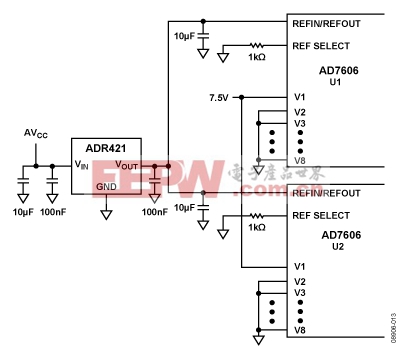

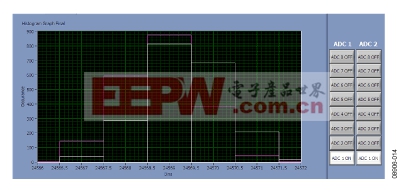

通道直方图的中心为码0,如图6所示。 基于16位8通道DAS AD7606的可扩展多通道同步采样数据采集系统(DAS)的布局考虑 (CN0148) 图5. 用于测试16通道系统通道间匹配的电路示意图,该系统采用两个AD7606和外部基准电压源ADR421,所有输入接地 图6. 图5所示电路的直方图,显示了使用外部基准电压源ADR421的16通道系统的通道间匹配性能 AD7606内部基准电压源用作系统基准电压源 AD7606内置一个2.5 V基准电压源,经过内部放大,它可以为AD7606 ADC提供约4.5 V的缓冲基准电压。在通道间和器件间匹配性能至关重要的高通道数应用中,可以用一个AD7606的内部基准电压源为另一个AD7606器件提供基准电压。在此配置中,U1配置为在内部基准电压下工作,如图7所示。 图7. 用于测试一个AD7606通道间匹配的电路示意图,使用U1内部基准电压源 AD7606 U2器件可配置为在外部基准电压源模式下工作。U1 REFIN/RFOUT引脚提供的2.5 V基准电压路由至U2的REFIN/REFOUT引脚。一个10 μF去耦电容位于AD7606器件的REFIN/REFOUT引脚。在AD7606 U1和U2上,REFCAPA和REFCAPB引脚短接在一起,并通过一个10 μF陶瓷电容去耦至GND。 两个AD7606器件均以200 kSPS的采样速率工作,一个7.5 V直流信号施加于U1的V1和V2,如图7所示。码的直方图如图8所示。在同一器件的通道之间,平均输出码相差1.2个码。板上的所有16个通道以200 kSPS速率进行转换。 图8. 图7所示电路的直方图 7.5 V信号施加于U1的V1和U2的V1,板上的所有16个通道以200 kSPS速率工作,如图9的配置电路示意图所示。码的直方图如图10所示。在不同器件的V1通道之间,平均输出码相差1.4个码。 图9. 用于测试两个AD7606之间器件间匹配的电路示意图,U1内部基准电压源用作系统基准电压源 图10. 图9所示电路的直方图 将一个AD7606的内部基准电压源用作系统基准电压源时,以上直方图显示,一个AD7606器件的通道之间以及多个器件的通道之间都具有非常好的匹配性能。 绝对精度 除了通道间匹配和器件间匹配外,如果ADC转换结果的绝对精度也非常重要,则应使用外部小容差、低漂移基准电压源作为系统基准电压源。在该电路中,ADR421 2.5 V基准电压源用作系统基准电压源。 施加于AD7606器件的基准电压会影响ADC输出码: 实际理想码的值会因温度而不同,具体取决于系统基准电压源的温度系数特性。在绝对精度非常重要的应用中,或者在希望避免通过复杂的温度校准程序实现绝对精度和通道匹配的应用中,应当使用ADR421等小容差、低漂移2.5 V基准电压源作为AD7606器件的系统基准电压源。 7.5 V直流电压施加于U1的输入(V1和V2),如图11的电路所示,并使用外部基准电压源。U1的两个通道的码直方图如图12所示。两个通道的码直方图平均值相差0.9 LSB。 图11. 用于测试一个AD7607通道间匹配的电路示意图,使用外部基准电压源 图12. 图11所示电路的直方图 在用于测试器件间匹配的图13所示电路中,7.5 V直流信号施加于U1和U2 AD7606器件的V1通道,并使用外部基准电压源。两个AD7606器件的两个V1通道的码直方图如图14所示。板上的所有16个通道以200 kSPS吞吐速率工作。U1和U2的V1通道之间的码直方图平均值相差0.6 LSB。 图13. 用于测试两个AD7606器件间匹配的电路示意图,使用外部基准电压源 图14. 图13所示电路的直方图 以上直方图显示,采用ADR421外部系统基准电压源时,一个AD7606器件的直方图平均值间匹配和多个AD7606器件的直方图平均值间匹配均小于1 LSB。 结论 本布局能够确保通过一个AD7606实现通道间良好匹配性能,并且同一PC板上的多个AD7606之间也具有良好的器件间匹配性能。AD7606器件的对称布局,特别是去耦电容将有助于实现良好的通道间匹配和器件间匹配。在高通道数系统中,良好的通道间和器件间性能匹配意味着校准程序得以简化。

- FPGA/CPLD与专用集成电路(ASIC)(06-06)

- 高级辅助驾驶系统:驾驶员应知应会(12-20)

- 高级车内系统的参考设计(12-16)

- 高可靠芯片搭配视觉演算法,影像式ADAS满足车规要求(12-14)

- 简述在汽车中导入ADAS的三大设计方式(12-12)

- 如何优化工业DAQ系统设计(12-12)