一种片内硬件调试支持单元设计

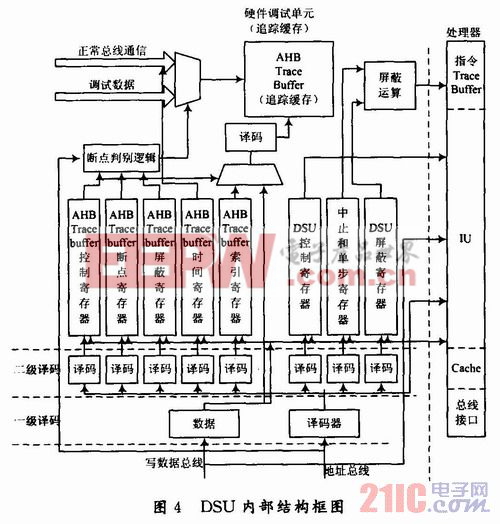

当DSU被AHB总线译码器选中后,DSU内部的第一级译码器将对地址总线访问地址进行译码,它将判断当前访问的对象属于三类存储单元中的哪一类,如果是第二类即DSU内部寄存器,那么将继续进行第二级地址译码,译码的结果将决定当前调试主机将访问哪一个功能寄存器;如果是第一类存储部件,由于它们容量较大,并需要其128 b的位宽能与总线位宽相兼容,所以需要在这些循环存储体内设计一个独立的译码器,能够对AHB索引寄存器或一级译码送出的地址再译码;对于第三类存储部件,由于此类存储部件位于DSU外部,所以除了需要DSU内部的第一、二级译码外,在处理器内部仍然需要更深层次的辅助译码,因此在实际工作中,访问此类存储单元所需的时钟周期要多于其他几类存储单元。在图4中,左边5个寄存器将共同决定AHB Trace Buffer的工作情况,断点判别逻辑根据控制、断点和屏蔽寄存器的内容共同决定AHB TraceBuffer记录值来源于总线还是调试主机;时间索引寄存器值将随时钟周期自增加,同时也作为记录内容的一部分方便以后查询;而索引寄存器也将随时钟周期自增,为正常通信数据提供地址,而在调试模式下,将由一级译码器直接提供访问地址;右边3个寄存器将共同控制

微处理器的工作状态,在DSU外部使能信号下处理器进入调试模式后,处理器将程序指针入栈保护,同时输出信号指示当前调试状态并将定时器冻结。当DSU控制寄存器中的BN位被清零时,则处理器定时器解冻,程序指针恢复,退出调试状态。

1.4 调试通信链路

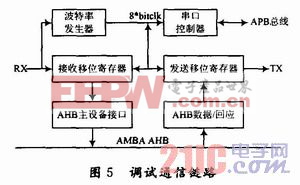

在图1中就已经提到在本系统设计中需要一个调试接口,该接口将连接调试主机与AHB总线,它包含一个连接在AHB总线上的专用UART。该系统为此设计了一个简单的通信协议,它支持数据在串口和AHB接口之间的格式转换。通过这个通信链路,一个读或写传输可以在任意的AHB地址上产生,其结构如图5所示。

该系统设计的UART包含一个波特率发生器,它利用一个18位宽的自减计数器产生所需的波特率,在时钟的驱动下,每当计数器下溢,则产生一个脉冲信号,同时将一个重载寄存器的预定值重新载入计数器,最终产生的UART脉冲频率将是所需波特率的8倍。

调试机的串口支持的数据帧结构为10位,包括1位起始位、8位数据位和1位停止位(高电平)。当进行的是读传输时,除了将读地址按照规定的帧格式进行拆分外,在开始阶段需另加1个控制帧,其中包含指明当前传输的类型以及连续传输的块数;若进行的是写传输,那么在地址发送完后,还需要按照帧结构发送调试数据。每次进行连续传输时,只需要发出1个首地址,以后地址将按照控制帧中指定的块数按字自增。

通过本接口,调试机的串行数据将能被此接口封装成符合AHB总线协议的传输格式,同样在读传输时,调试输出数据也能被此接口分解为单bit数据返回到调试串口。

2 结语

当今业界已经出现了较为成熟的硬件调试系统,如ARM公司的基于JTAG的Embeded ICE宏单元和Multi-ICE协议转换器,它通过扩展JTFAG测试端来实现通信,利用扫描链插入技术访问寄存器并向处理器施加指令来访问处理器及系统的状态。但是由于安全和商业因素的原因,ARM及其调试工具提供商都没有公开它们的细节,并且其高昂的价格也使得很多用户对其望而却步。本文所提出的一种硬件调试单元完全自主实

现,且顺利通过Modelsim的功能仿真,所以它不但能够有效的完成对片上处理器的诊断与调试,而且其拥有的跟踪技术也能对程序的运转以及片内的通信状况进行实时监控,同时专用的硬件协议转换模块在片内就实现了远程调试连接,能够方便的与调试机进行通信。

嵌入式 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)