逻辑分析仪SignalTaPⅡ在系统级调试中的应用

摘要:嵌入式逻辑分析仪SignalTap II是Quartus II软件中第二代系统级调试工具,它可以用来捕捉目标芯片内部信号节点处的信息,而又不影响原硬件系统的正常工作。通过一个多波形信号发生器的设计实例,详细阐述SignalTap II的工作流程和参数设置方法。实验结果表明,该测试方法操作方便,实时性较高,能够加快系统的开发流程。

关键词:SignalTap II;测试;信号发生器

引言

随着微电子技术、微封装技术和印制板制造技术的不断发展,印制电路板面积越来越小,密度越来越大,复杂度越来越高,层数越来越多。故采用传统的硬件测试方法(如外探针测试法)来测试焊接上的器件,难度增大。而嵌入式逻辑分析仪的使用可以将高效的硬件测试手段和传统的系统测试方法相结合,从而解决这些问题。嵌入式逻辑分析仪实现了硬件测试的软件化,但它和验证逻辑正确性的软件仿真又有所不同。它可以用来捕捉目标芯片内部信号节点处的信息,而又不影响原硬件系统的正常工作,具有无干扰、便于升级、使用简单、价格低等特点。

1 SignalTap II原理及工作流程

SignalTap II逻辑分析仪是Quartus II软件中第二代系统级调试工具。它是一种基于逻辑分析核的嵌入式逻辑分析仪,不仅具备普通逻辑分析仪的触发、数据采集和存储功能,还可访问FPGA器件内部的所有信号和节点,在系统设计中观察硬件和软件的交互作用。SignalTap II专用于Quartus II软件,与其他嵌入式逻辑分析仪相比,它支持的通道数最多,抽样深度最大,时钟速率最高。目前SignalTap II逻辑分析仪支持的器件系列包括:Cyclone、Cyclone II、Cyclone III、APEXT II、APEX 20KE、APEX20KC、APEX20K、Excalibur、Mercury、Stratix GX、Stratix、Stratix II、Stratix III等。

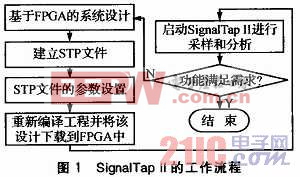

SignalTap II的工作流程如图1所示。在FPGA运行过程中,当满足触发条件时SignalTap II将启动采样过程并将数据暂存于目标器件中的嵌入式RAM(如ESB、M4K)中,采样数据不断刷新片内存储器内容,然后通过器件的JTAG端口将捕获到的信号数据传出,送入计算机Quartus II开发环境中进行显示和分析。这样开发者可以在整个设计过程中以系统级的速度来观察硬件和软件的交互作用。此外,SignalTap II允许对设计中的所有层次的模块的信号节点进行测试,可以使用多时钟驱动,而且还能通过设置以确定前后触发捕捉信号信息的比例。

在图1所示的SignalTap II工作流程中,STP文件的参数设置是否恰当将直接影响采样与分析结果的好坏,故它在整个流程中是极其重要的。STP文件的参数设置主要包括以下几个方面:

①设置采样时钟。采样时钟决定了显示信号波形的分辨率,它的频率要大于被测信号的最高频率,否则无法正确反映被测信号波形的变化。SignalTap II在时钟的上升沿采样,可以使用设计系统中的任何信号作为采样时钟,根据Altera公司的建议最好使用同步系统全局时钟

作为采样时钟。但是在实际应用中,多数使用独立的采样时钟,这样能采样到被测系统中的慢速信号,故需将系统时钟进行分频。

②设置被测信号。可以在Node Finder窗口进行选择,添加要观察的信号。

③配置采样深度,确定RAM的大小。采样深度决定了待测信号采样存储的大小,它是根据设计中剩余的RAM块容量和待测信号的个数决定的。待测信号个数的增减和采样深度的深浅会直接改变RAM块的占用情况,采样深度的范围为0~128 KB。SignalTap II所能显示的被测信号波形的时间长度为Tx=N×Ts,其中N为缓存中存储的采样点数,Ts为采样时钟的周期。

④设置buffer acquisition mode。buffer acquisitionmode包括循环采样存储、连续存储两种模式。循环采样存储也就是分段存储,将整个缓存分成多个片段(segment),每当触发条件满足时就捕获一段数据。该功能可以去掉无关的数据,使采样缓存的使用更加灵活。通常选择循环采样存储,需要设置触发位置。触发位置允许指定在选定实例中在触发器之前和触发器之后应采集的数据量。Pre trigger position表示采样到的数据12%为触发前,88%为触发后;Center trigger position表示采样的数据处于触发前后各一半;Post trigger position表示采样到的数据88%为触发前,12%为触发后;Continuous triggerposilion表示以环形缓冲的方式进行连续采样保存,直到用户中断为止。

⑤触发级别。SignalTap II支持多触发级的触发方式,最多可支持10级触发,为设置复杂的触发条件提供了足够的灵活性,帮助验证检错。如果设置了多触发级别,直到所有的触发条件顺序满足后,才开始采集数据。

⑥触发条件。设定约束性的触发条件。可以设定单个信号的独立触发条件,直接采用单个外部或设计模块内部的信号;也可以允许多个节点信号的组合复杂触发条件构成触发函数的触发条件方程,以协助调试工作。当触发条件满足时,在SignalTap II时钟的上升沿采样被测信号。例如,使能信号EN与RST相与后触发,触发条件=ENARST。

当完成以上设置后,重新编译工程并将该设计下载到FPGA中,在Quartus II中SignalTap II窗口下查看逻辑分析仪捕获结果,并进行相关分析,完成系统测试。

调试 应用 系统 SignalTaP 分析仪 逻辑 相关文章:

- 嵌入式LINUX系统的静/动态集成调试模式 (07-03)

- 嵌入式软件中基于栈的错误追踪机制设计(08-03)

- 基于RTOS的嵌入式系统在Nexar中的实现(01-20)

- 基于DSP TMS320F206的仿真调试 (07-06)

- 总线实现片内硬件调试支持单元设计(08-15)

- 多核处理器架构及调试方案(03-28)