DS2450转换器的接口设计原理

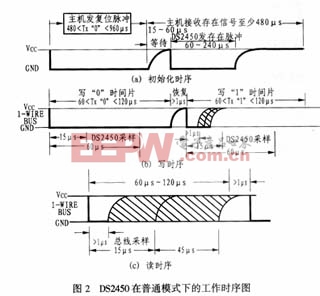

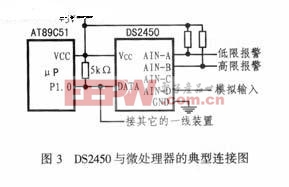

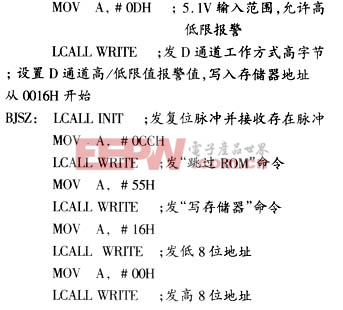

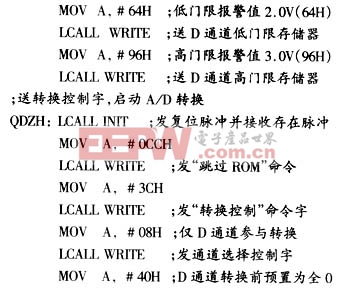

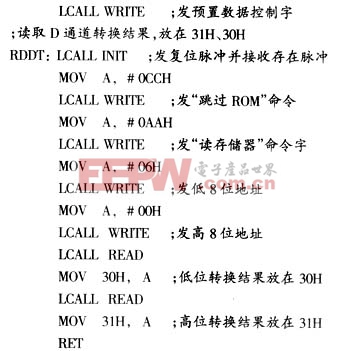

发现读/写中的传输错误,则必须对DS2450芯片进行初始化,并重新进行读/写操作。 2.3 DS2450的工作时序 DS2450的一线工作协议流程是:初始化→ROM功能命令→存储器读写/转换控制功能命令→传输数据。其工作时序包括初始化时序、写时序和读时序,图2给出了普通工作模式下的工作时序。 3 DS2450与单片机的典型接口设计 图3是MCS-51系列单片机与DS2450的典型连接电路。其中DS2450的DATA端接AT89C51的P1.0,该电路采用外接电源供电方式,其DS2450的VCC端用 5V电源供电。此例仅对D通道进行A/D转换,AIN-D接模拟信号输入;AIN-A和AIN-B外接上拉电阻到电源,其输出可作为D通道的高、低限报警信号。 如果单片机系统所用的晶振频率为12MHz,那么可根据DS2450的初始化时序、写时序和读时序来分别编写三个子程序:其中INIT为初始化子程序,可用于发送复位脉冲并接收存在脉冲;WRITE为写(命令或数据字节)子程序;READ为读数据子程序。所有要读写的命令或数据字节均被放在A寄存器中。 通过主机控制DS2450来完成A/D转换一般要经过以下几个步骤:初始化、发ROM功能命令和相应的64位光刻ROM数据、选中特定芯片、写入工作方式控制字和高/低限门限值、发转换控制命令、读取转换值及状态等。 如果将D通道设定为5.1V输入范围,转换精度为12位,高报警门限为3.0V(96H),低报警门限为2.0V(64H),并将通道A和通过B作为报警输出,最后将转换结果放在30H和31H处,那么其子程序CTLAD的具体程序清单如下: CTLAD:LCALLINIT;发复位脉冲并接收存在脉冲 如果一线上挂接有多个DS2450以及其他单总线接口芯片,那么采用寄生电源供电和超速模式工作且要求在通讯中进行校验的子程序CTLAD的编写可能会复杂一些。

- 嵌入式编程需注意的Cache机制及其原理(05-25)

- 通信系统原理技术与DSP实验平台的研制(06-06)

- Linux 环境下USB 的原理、驱动和配置(06-06)

- 基于FPGA的原型板原理图的验证(06-05)

- CAN总线原理介绍(12-16)

- 直流无刷电动机原理与控制(12-15)