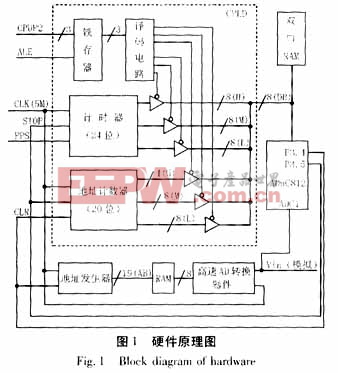

高速数据采集系统中精确时标的CPLD实现方法

2.1 ADuC812的工作过程 4 结论

ADuC812初始化时P3.5置“0”,同时P3.4发出清零脉冲使地址发生器和地址计数器同步计数。ADuC812控制内部的ADC转换模块对经过调整的取自电流互感器二次侧的电流进行AD转换,采用半波比较,在每个工频内采集36个点,分别用第n个点和第n+18个点、第n+1个点和第n+19个点比较,依此类推,如果大于事先设定的门槛值即认为故障已经发生。ADuC812使P3.5置“1”,计时器和地址计数器同时停止计数,计时器中的数据即为地址计数器记录的对应于静态RAM相同地址采集数据的时间标签,由于高速AD转换器件的转换频率固定(本次设计为5MHz),所以,可以此为基准为整个静态RAM中的采集数据贴上时间标签。

3.2 计时器和地址计数器的工作过程

当STOP端口为低电平时(P3.5置“0”),计时器在5MHz的时钟源下以相同的频率计数,由于它是一个24位的计数器,从而确保了计时器能够记录一个整秒,并为一个整秒刻上了 =0.2μs)的最小刻度。同时GPS发出的1PPS信号的上跳沿给计时器清零,从而为计时器提供精确的时间基准,以消除计时器的累计误差。

=0.2μs)的最小刻度。同时GPS发出的1PPS信号的上跳沿给计时器清零,从而为计时器提供精确的时间基准,以消除计时器的累计误差。

当STOP端口为高电平时(P3.5置“1”),计时器停止计数,在此状态下GPS发出的1PPS信号的上跳沿不能对计时器清零。

地址计数器的工作过程与计时器的工作过程类似,唯一的区别是地址计数器的清零信号(CLR)是在初始化时由ADuC812的P3.4口发出的,由于地址发生器和地址计数器共用同一个清零信号,从而确保地址发生器和地址计数器中的计数值完全相同。同理当STOP端口为高电平时,地址计数器也停止计数,在此状态下ADuC812发出的清零信号不能改变地址计数器中的计数值。

2.3 将地址计数器和计时器中的数据送至双口RAM

由于ADuC812是一种8位单片机,所以地址计数器和计时器中的数据只能“分批”地送至双口RAM中保存。所以要设计锁存器、译码电路和总线隔离电路,避免总线冲突以及保证总线上的数据能正确无误地传递。在本次设计中,当ADuC812的特殊功能寄存器DPP高3位的值为“00H”时将计时器的高8位数据通过ADuC812送至双口RAM中,依此类推,当特殊功能寄存器DPP高3位的值为“05H”时将地址计数器的低8位数据通过ADuC812送至双口RAM中保存。当特殊功能寄存器DPP为其他值时释放数据总线,便于ADuC812进行其他操作。

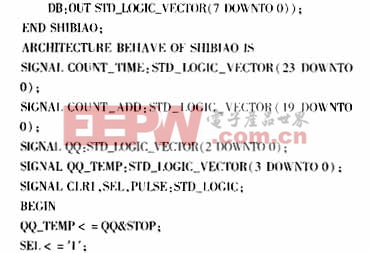

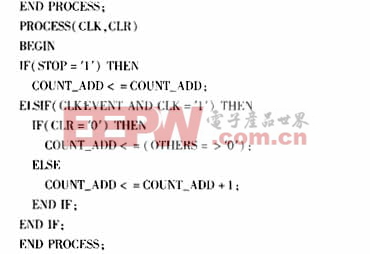

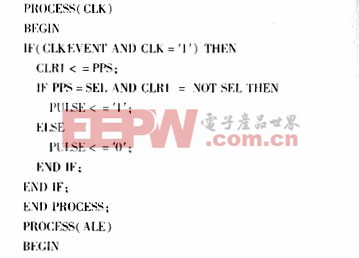

2.4 系统的VHDL描述及其仿真结果

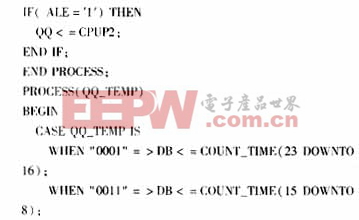

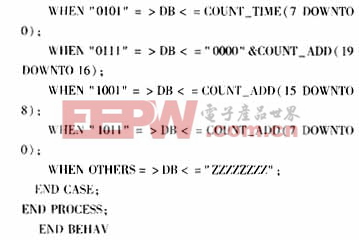

系统的上述功能可由硬件描述语言(VHDL)来实现,源程序如下:

其仿真结果如图2所示。

本文对高速数据采集系统中的采集数据贴上精确时间标签的方法进行了详细地叙述和仿真,得出如下结论:

(a) 假设高速AD转换器件的转换频率为5MHz,则本系统能为存入静态RAM中的转换数据贴上精度为0.2μs的时间标签。

(b) 通过复杂可编程逻辑器件(CPLD)间接地实现了“低速”的单片机系统对高速数据采集系统的实时监视。

CPLD 实现 方法 标的 精确 数据采集 系统 高速 相关文章:

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 基于DSP+CPLD的交流电机调速在水处理控制中的应用(11-27)

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于DSP和CPLD的宽带信号源的设计(07-26)